Description and Features

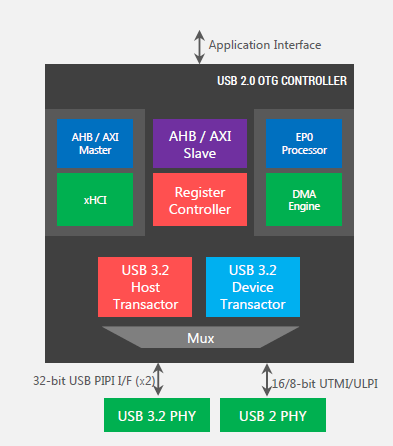

USB 3.2 OTG controller are designed for compliance with USB 2.0 specification Revision 2 0 and all associated ECN’s and USB OTG EH 2 Revision 1.1a and all associated ECN’s While operating in Host mode, based on configuration selected, it is compliant with xHCI enabling standard Windows, Linux, Android drivers to be reused minimizing software development overheads and associated risks involved with custom bare metal driver solutions Its Physical interface is compliant with USB Pipe Specification v 4 3 (for SS/SSP lane rates) and ULPI+ or 8 16 bits UTMI PLUS Level 3 specification (for HS/FS/LS mode) The system interface is compliant with either AHB and/or AXI interface allowing easy integration Optional custom bridges can be bundled as a service offering.

USB 3.2 OTG controller, while operating in device mode, can optionally include a proprietary high performance DMA engine for moving USB payloads The register interface of the DMA Engine is very simple allowing device side class specific function drivers to be implemented easily Reference mass storage class device side function drivers are made available to all licensees All buffering associated with the DMA Engine are configurable based on latency and performance requirements.

Features

-

USB 3.2 OTG Controller can be configured to support all types of USB transfers Bulk, Interrupt and Isochronous While operating in Device Mode it can be dynamically configured to support configurable number of endpoints,interfaces, alternate interfaces and configurations While operating in host mode, it can optionally be configured to support hubs

-

USB 3.2 OTG Controller can be configured to support any combinations of USB 3.2 interface speeds 20 Gbps 10 Gbps (x 1or x 2 5 0 Gbps USB 2 0 Speeds

-

USB 3 2 OTG Controller has full support for all low power features of the USB Specification supporting Suspend, Remote Wakeup and USB 3.0 Link Management States U 1 U 2 U 3 and USB 2 0 Link Power Management states L 1 L 2

-

USB 3.2 OTG controller has full support for all USB 2.0 test modes features as well as USB 3.0 compliance and USB 3.0 loopback modes which is required for obtaining USB IF certification

-

USB 3.2 OTG Controller has support for OTG features such as RSP, SRP, HNP and ADP along with software configurable options to turn on/off these features

-

USB Controllers have been Silicon Proven in wide range of products such as Graphics Controller, Flash Storage Controllers,

-

SATA Bridges with support for Bulk Streaming, Embedded Hosts,

-

Docking Stations, Mobile Application Processors, Smart TV, Hubs

-

USB OTG Controller IP core is compatible with USB 3.2 specification Revision 1.0 and all associated ECN’s

-

USB OTG Controller IP core is compatible with USB specification Revision 2.0 and all associated ECN’s

-

USB OTG Controller IP core compatible with USB OTG EH 3.0 Revision 1.1 and all associated ECN’s

-

USB OTG Controller IP core compatible with USB OTG EH 2 Revision 1.1 a and all associated ECN’s

-

USB OTG Controller IP core operating in host mode is compliant with xHCI specification version 1.1

Benefits

-

Fully compliant to USB 3.2 specifications

-

Highly flexible and configurable

-

USB Controllers have been Silicon Proven in wide range of products

-

USB 3.2 OTG Controller has support for OTG features such as RSP, SRP, HNP and ADP along with software configurable options to turn on/off these features

Applications

-

Scanners

-

Digital cameras

-

Removable media drives

-

Mass storage devices

-

Display and docking applications

-

Cloud computing

-

Automotive applications

-

Consumer applications

Deliverables

-

Flexible RTL Configuration

-

HDL-based Test Bench with Behavioral Models

-

Test Case Suites

-

Protocol Validation Modules, Bus Observers, and Performance Monitors

-

Customizable Synthesis Framework

-

Design Handbook

-

Verification Manual

-

Synthesis Procedure Guide

-

FPGA Validation Platform for Pre-Tape-out Testing

-

Firmware Reference Implementation

![]()