Description and Features

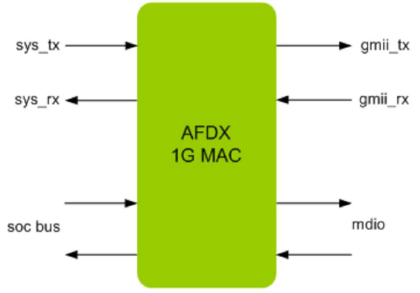

AFDX 1G MAC core is a full-featured, easy-to-use, synthesizable design that supports various Ethernet IEEE standards, ARINC 664 and supports 10/100/1000M speeds. Through its Ethernet compatibility, it provides a simple interface to a wide range of low-cost devices. AFDX 1G MAC IP is proven in FPGA environment. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses. AFDX 1G MAC IP is supported natively in Verilog and VHDL.

Features

-

Compliant with ARINC 664 Specification

-

Compliant with IEEE Standard 802.3-2018 for 10/100/1000M Specification.

-

Supports Pre-emption as per IEEE Standard 802.1Qbu and IEEE Standard

-

802.3br Interspersing Express Traffic

-

Supports timing synchronization as per IEE Standard 1588-2008(PTP)

-

Supports Traffic Scheduling - IEEE Standard 802.1Qbv and IEEE Standard 802.1Qav

-

Supports Frame Replication and elimination as per IEEE 802.1CB

-

Supports class-based flow control and class-based FIFO to store each class, total 8 class - IEEE Standard 802.1Q

-

Supports for Full duplex Ethernet Link

-

Supports Virtual Link Traffic Shaping (BAG – Bandwidth Allocation Gap)

-

Ultra-low latency and compact implementation

-

Supports for MDIO (Clause 22 and Clause 45) Interface

-

Supports for Programmable Inter Packed Gap (IPG) and Preamble length

-

Support GMII/RGMII/MII interface

-

FCS generation supported

-

Independent TX and RX Maximum Transmission Unit (MTU)

-

TSN features can be enabled/disabled independently

-

Cut-through support

-

Configurable Transmit and Receive FIFOs

-

Provides detailed statistics as per the specification including VL (Virtual Link) message count

-

Supports 32bit AXI4 Stream for Packet data

-

Optional DMA support for both transmit and receive side

-

In house UNH compliance tested

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices

Deliverables

-

The AFDX interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes

![]()