Description and Features

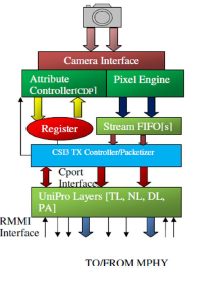

CSI3 is a high speed serial interface protocol for integration of camera subsystems such as RAW image sensors, SOC cameras, Image Signal Processors (ISP) and bridge devices with host processor such as an application processor in mobile terminal application. MPHY is the PHY layer used in CSI3 system and UniPro is the link layer used for connection management and transferring of pixel and managing link. UniPro specification defines a layered protocol for interconnecting Devices and components within mobile systems such as cellular phones, handheld computers, digital cameras and multimedia devices. UniPro enables these devices and components to utilize MIPI PHY layers in order to exchange data at high data rates with low pin counts and at low energy per transferred bit. MPHY is the PHY layer to transfer the symbols across chips connected through UniPro protocol. Upto 4 lanes per direction can be used which would provide a very high speed serial data transfer across chips.

Features

-

Compliant with MIPI CSI3 V1.0, MIPI M-PHY spec v2.0. MIPI UniPro Spec v1.8

-

Upto 4 MPHY lanes configurable per direction [10Mbps – 5.8Gbps per lane supported].

-

One dedicated CPORT for CPC and 2 CPORT for Pixel/embedded data transmission supported.

-

CPC GET/SET/NOTIFY/RESPONSE PDU Processing supported.

-

Host capable of receiving CPC NOTIFY transmitted with Pixel transport channels and Notification channels.

-

Support of Embedded data during vertical blanking period.

-

E2E support for CPC packets and E2E disable option[and CSD enable option] for CPORTS used for transmitting Pixel and Embedded data.

-

Round Robin Arbitration across CPORTS to handle different VCID’s.

-

Camera and Host streaming supported.

-

TX Buffer overflow management supported.

-

Preemption frame handling by host and device.

-

Interleaving of pixel data from two different Sources supported.

Deliverables

-

Configurable RTL Code

-

HDL-based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers, and performance monitors

-

Configurable synthesis shell

-

Documentation

-

Design guide

-

Verification guide

-

Synthesis guide

Benefits

-

Highly modular design

-

Fully synchronous design

-

Configurable IP.

Applications

-

Camera

-

Automotive

-

Consumer

![]()