Description and Features

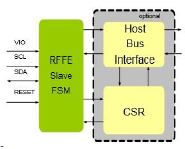

The MIPI RFFE Slave Controller IP Core is a full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The RFFE Slave controller IP can be implemented in any technology. The Slave controller IP core supports the MIPI RFFE 3.0 standard. It can also support a variety of host bus interfaces for easy adoption into any design architecture – AXI, AHB, APB, OCP, VCI, Avalon, PLB, Wishbone or custom buses. The Slave IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The Slave IP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Compliant with version 3.0 MIPI RFFE Specifications.

-

Full MIPI RFFE Slave Functionality.

-

Supports following frames

-

Command Frame

-

Data/Address Frame

-

No Response Frame

-

Supports extended register read/writes

-

Supports interrupt summary and identification command sequence

-

Support Trigger and Extended trigger modes

-

Support Masked write command sequence

-

Support Synchronous read

-

Support Normal and Secondary operation mode

-

Support USID Programming Procedure 1,2 and 3

-

Supports Group Slave ID

-

Supports Broadcast Writes to PWR_MODE, TRIG_REG, EXT_TRIG_REG and other registers

-

Supports device enumeration

-

Supports Half-Speed Data Response (HSDR) Accesses

-

Supports Full Command Sequence at Half-Speed SCLK

-

Supports Delayed Read-back

-

Supports Reserved Register Allocations in Basic Address Space (0x1C – 0x1F)

-

Supports Reserved Register Allocations in Extended Address Space (0x20 – 0x3F)

-

Supports Write Slave State via PWR_MODE bits

-

Supports Read Slave State via PWR_MODE bits

-

Supports Read PRODUCT_ID, MANUFACTURER_ID and USID from reserved registers.

-

Undefined command frame

-

Fully synthesizable

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Optionally this core can be built to have SPI or I2C interface for application where slave can have multiple interfaces like RFFE or SPI or I2C Interface

Deliverables

-

RTL design in Verilog

-

Lint, CDC, Synthesis Scripts with waiver files

-

Lint, CDC, Synthesis Reports

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Technical documentation in greater detail

-

Easy to use Verilog Test Environment with Verilog Testcases

Benefits

-

Fully compliant, silicon-proven core

-

Comes with Verilog testbench and option to buy full advanced System Verilog Testbench

-

Support directly from engineer who designed the code.

-

Based on RMM (ReUse Methodology Manual guidelines)

-

Supports all the Synthesis tools

![]()