Description and Features

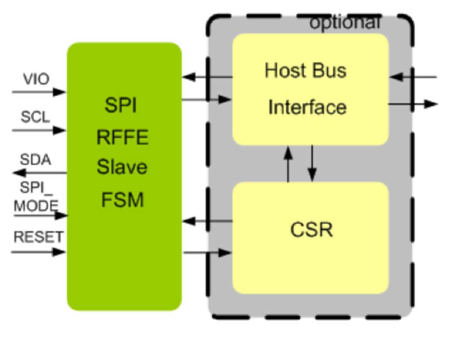

MIPI RFFE SPI Slave interface provides full support for the two-wire MIPI RFFE synchronous serial interface with SPI overlay, compatible with RFFE 2.1 and SPI Block Guide V04.01 specification. Through its RFFE compatibility, it provides a simple interface to a wide range of low-cost devices. MIPI RFFE SPI Slave IP is proven in multiple ASIC. The host interface of the MIPI RFFE/SPI can be simple interface or can be AMBA AHB, AMBA AHB-Lite, AMBA APB, AMBA AXI, AMBA AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom protocol.

Features

-

Compliant with 3.0 MIPI RFFE Specification and SPI

-

Block Guide V04.01 Specification

-

Full MIPI RFFE Slave functionality.

-

Supports following frames • Command Frame • Data/Address Frame • No Response Frame

-

Supports extended register read/writes

-

Supports interrupt summary and identification command sequence

-

Support Trigger and Extended trigger modes

-

Support Masked write command sequence

-

Supports Timed Trigger

-

Supports Mappable Triggers

-

Support Synchronous read

-

Support Normal and Secondary operation mode

-

Support USID Programming Procedure 1,2 and 3

-

Support Group slave ID

-

Supports device enumeration

-

Supports Half-Speed Data Response (HSDR) Accesses

-

Supports Full Command Sequence at Half-Speed SCLK

-

Supports Delayed Read-back

-

Supports Reserved Register Allocations in Basic Address Space (0x1C – 0x1F)

-

Supports Reserved Register Allocations in Extended Address Space (0x20 – 0x3F)

-

Supports Write Slave State via PWR_MODE bits

-

Supports Read Slave State via PWR_MODE bits

-

Supports Read PRODUCT_ID, MANUFACTURER_ID and USID from reserved registers.

-

Support Interrupt capable slave

-

Supports Extended Frequency Range up to 52 MHz

-

Supports the following Error detections • Undefined command frame • Command frame with parity error • Command frame length error • Address frame with parity error • Data frame with parity error

-

Read and Writ of unused register

-

Read using the broadcast ID or a GSID

-

Full SPI Slave functionality

-

Supports following frames for SPI • Sleep Frame • Wakeup Frame • Write Frame • Read Frame

-

Supports 8 bit and 16 bit address for SPI.

Deliverables

-

The MIPI RFFE SPI Slave interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()