Description and Features

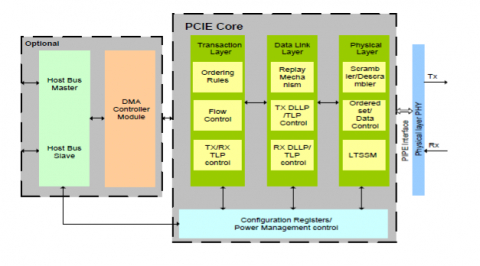

The Peripheral Component Interconnect Express Controller IP Core is full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The PCIE Controller IP can be implemented in any technology. The PCIE Controller IP core supports the PCI 5.0 Specification. It can also supports a variety of host bus interfaces for easy adoption into any design architecture – AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol. The PCIE Controller IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The PCIE Controller IIP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Compliant with PCIE 1.0/2.0/3.0/4.0/5.0 Specifications

-

Full PCIE Controller functionality

-

Supports PIPE interface.

-

Compatible with Gen1,2,3,4 and 5

-

Supports following BFM modes

o Root Complex

o Endpoint

-

Supports queuing for 8 Virtual Channels with configurable depth Supports up to 8 Traffic Classes

-

Supports multi-function Configurable TC to VC queue mapping

-

Supports full link speed and width negotiation up to 8 Lanes

-

Supports up to 32 bits pipe width

-

Supports MSI/MSI-X Interrupts

-

Multiple Requester / Completer applications, including user supplied applications

-

User interface for direct TLP queuing and receipt

-

Check all TLPs for correct formation of headers, prefixes, and ECRC

-

Supports full DL state machines

-

Check all framing, LCRC, and lane rules

-

Check all DLLP fields and formatting

-

Supports ASPM and Software controlled Power Management Supports full LTSSM state machine

-

Supports Speed and Link Width negotiation

-

Supports Up configure, polarity inversion, and lane-to-lane skew Configurable timers and timeouts

-

Supports Scaled Flow Control

-

Supports Data Link Feature Exchange

-

Supports Lane Margining at Receiver

-

Supports vF 10-Bit Tag Requester

-

Supports enhanced Allocation

-

Supports emergency Power Reduction State

-

Supports DMA(optional)

-

Fully synthesizable. Static synchronous design.

-

Positive edge clocking and no internal tri-states.

-

Scan test ready.

-

Simple interface allows easy connection to microprocessor/microcontroller devices.

Benefits

-

Fully compliant, silicon-proven core

-

Comes with Verilog test bench and option to buy full advanced System Verilog Test bench

-

Support directly from engineer who designed the code.

-

Based on RMM (Re Use Methodology Manual guidelines)

-

Supports all the Synthesis tools.

Applications

-

PC

-

Digital TV

-

Set-top boxes

-

Enterprise computing, storage area networks, networking switches, and routers

-

Wireless and mobile devices

-

Industrial, automotive, and IoT

-

Embedded systems

-

Graphics devices

-

Laptops

-

Workstations

-

Servers

Deliverables

-

RTL design in Verilog

-

Lint, CDC, Synthesis Scripts with waiver files

-

Lint, CDC, Synthesis Reports

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Technical documentation in greater detail

-

Easy to use Verilog Test Environment with Verilog Test cases.

![]()