Description and Features

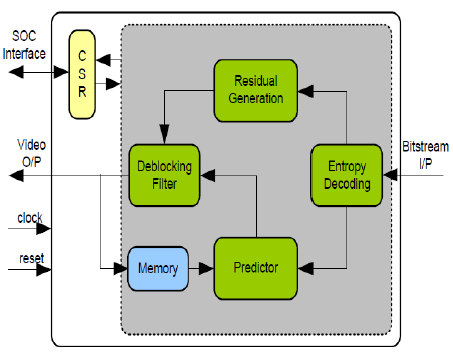

The H.265 Decoder IP Core is a full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The H.265 Decoder IP can be implemented in any technology. The H.265 Decoder core supports the ISO/IEC 23008-2/ITU-T H.265 specification. It can also supports a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses. The H.265 Decoder IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The H.265 Decoder IP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Supports ISO/IEC 23008-/ITU-T H.265 specification.

-

Supports full H.265/HEVC Decoder functionality.

-

Supports profile level up to 6.2.

-

Supports resolution up to 3840x2160@60fps.

-

Supports adaptive deblocking and sample adaptive offset filters.

-

Supports CABAC entropy decoding.

-

Supports all prediction methods • Inter prediction • Intra prediction

-

Supports 32x32, 16x16, 8x8 and 4x4 integer DCT Transform

-

Supports Chroma 4:4:4, 4:2:2 and 4:2:0

-

Supports VBR and CBR. Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to microprocessor/microcontroller devices

Deliverables

-

RTL design in Verilog.

-

Lint, CDC synthesis script with waiver files.

-

Lint, CDC synthesis reports.

-

IP-XACT RDL generated address map.

-

Firmware code and Linux driver package.

-

Technical documentation in greater detail.

-

Easy to use Verilog test environment with Verilog test cases.

Benefits

-

Fully compliant, silicon-proven core.

-

Comes with Verilog testbench and option to buy full advanced System Verilog Testbench

-

Support directly from engineer who designed the code.

-

Based on RMM (Re Use Methodology Manual guidelines).

-

Supports all the Synthesis tools

![]()