Description and Features

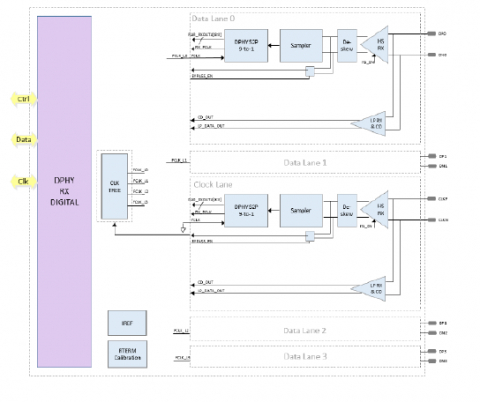

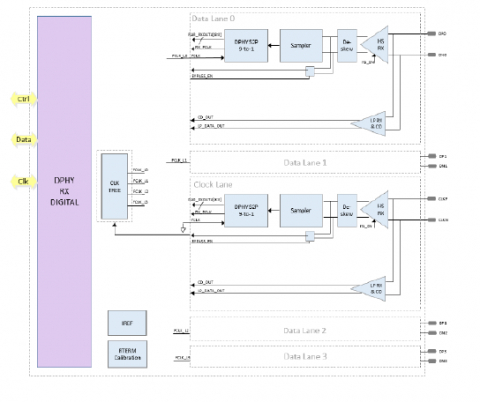

The MIPI D-PHY Analog RX IP Core is fully compliant to the D-PHY specification version 1.2. It supports the MIPI Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols. It is a RX PHY with one clock lane and 4 data lanes.

The D-PHY consists of an analog front end to generate and receive the electrical level signals, and a digital back end to control the I/O functions. Internal termination resistor with auto-calibration.

Features

-

Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

-

Supports standard PPI interface compliant to MIPI Specification

-

Supports synchronous transfer at high speed mode with a bit rate of 80-2500 Mb/s

-

Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

Supports ultra low power mode, high speed mode and escape mode

-

Supports one clock lane and up to four data lanes

-

Data lanes support transfer of data in high speed mode

-

sequence errors and contentions

-

Supports contention detection

-

Configurable skew option for each Clock and Data lanes.

Deliverables

-

GDSII & layer map

-

Place-Route views (.LEF)

-

Liberty library (.lib)

-

Verilog behavior model

-

Netlist & SDF timing

-

Layout guidelines, application notes

-

LVS/DRC verification reports

Applications

-

PC, Television

-

Data storage

-

Multimedia Devices

-

Recorders

-

Mobile devices