Description

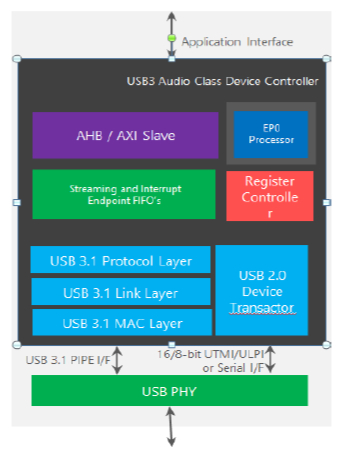

USB 3.0 Audio Class Device controller are designed for compliance with USB Audio 3.0 Specification, USB3.1 specification, Revision 1.0 and all associated ECN’s, USB specifications Rev 2.0 and all associated ECN’s. USB3.0 Audio Class Device controller can optionally include a proprietary EPO processor block for managing all Standard Requests directed to the control endpoint minimizing software development overhead. Class and Vendor specific requests directed to Control endpoint are routed via a simple slave register access interface to software for processing. USB Audio Class Device Controller provides a simple AHB interface to allow user logic to forward the audio data to the IP. The controller handles all USB specific packetizing for USB Audio Class applications. It provides reference firmware which can be reused by customer to build the relevant device side firmware for managing the audio control transfers based on Audio3.0 Specification.

Features

-

USB3 Audio Class Device Controller can be dynamically configured to support configurable number of endpoints, alternate interfaces, and configurations

-

USB3 Audio Controller can be configured to support any combinations of USB3 Audio Controller can be configured to support any combinations of USB3.1 interface speeds–SSP(10Gbps),SS(5Gbps),HS(480Mbps),FS(12Mbps).Eg combinations are SSP & SS only,SSP & SS & HS only,SSP & SS & HS & FS only,SS Only,SS & HS Only,SS & HS & FS Only etc

-

USB3 Audio Class Controller has full support for all low power features of the USB Specification supporting Suspend and Remote Wakeup,USB3.1 Low Power States–U1/U2/U3 and USB2.0 Link Power Management states–L1,L2

-

USB3 Audio Class Controller has multiple power domain support as specified in the Audio3.0 Specification

-

USB3 Controllers have been silicon proven in wide range of products such as Graphics Controller,Flash Storage Controllers,SATA Bridge switch support for Bulk Streaming, Embedded Hosts, Docking Stations, Mobile Application Processors,SmartTV,Hubs

Benefits

-

Highly modular and configurable design

-

Layered architecture

-

Fully synchronous design

-

Supports both sync and async reset

-

Clearly de-marked clock domains

-

Extensive clock gating support

-

Multiple Power Well Support

-

Software control for key features

Applications

-

Embedded Hosts

-

Docking Stations

-

Mobile Application

-

Smart TV

-

Hubs

Deliverables

-

Customizable RTL Coding

-

HDL-based Test Bench with Behavioral Models

-

Test Case Repository Protocol Compliance Checkers, Bus Monitors, and Performance Analyzers

-

Configurable Synthesis Framework

-

Design Handbook

-

Verification Manual

-

Synthesis Procedure Guide

-

FPGA Validation Platform for Pre-Tape-out Testing

-

Firmware Reference Implementation and Documentation

![]()