Description

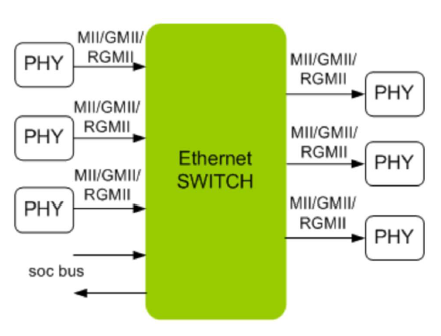

Ethernet Switch core is a full-featured, easy-to-use, synthesizable design that supports various Ethernet IEEE standards. Through its Ethernet compatibility, it provides a simple interface to a wide range of lowcost devices. Ethernet Switch IP is proven in FPGA environment. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses.

Features

-

Compliant with IEEE Standard 802.3-2018 Specification

-

Supports Full-duplex and Half-duplex 10M/100M/1G Ethernet interfaces

-

Supports 10G/25G/50G/40G and 100G Ethernet interfaces

-

Supports MII/GMII/RGMII/QSGMII/USXGMII Physical Layer device (PHY) interfaces

-

Supports different data rate for each port

-

Supports Dynamic MAC Table with automatic MAC addresses learning and aging

-

Supports Static MAC Table

-

Supports Jumbo Frame Management

-

Supports Ethertype Based Switching

-

Supports Ingress Port Mirroring

-

Supports Broadcast/Multicast Storm protection

-

Supports Per-Port Rate limiting (Broadcast, Multicast and Unicast traffic)

-

Supports timing synchronization as per IEEE Standard 1588-2008(PTP)

-

Supports Multicast Frame Filtering

-

Supports Switching Portmask

-

Supports Port-based VLAN

-

Supports QoS - Priorities (PCP-802.1p,DSCP TOS, Ethertype)

-

Supports DSA (Distributed Switching Architecture) tagging

-

Supports MDIO, AXI4-Lite or CoE(Configuration-over- Ethernet) SOC interfaces

-

Supports RSTP (Software stack required)

-

Supports MRP (Software stack not required) • Ring Manager (MRM) • Ring Client (MRC)

-

Supports DLR (Software stack not required) • Beacon Based Node • Supervisor Node

-

In house UNH compliance tested

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices.

Deliverables

-

Verilog RTL design

-

Seamlessly integrating waivers into validation scripts to ensure comprehensive coverage of Linting, CDC analysis, and Synthesis

-

Provision of detailed and comprehensive reports providing profound insights into Linting, CDC analysis, and Synthesis methodologies

-

Efficiently utilizing IP-XACT RDL for generating address maps

-

Consolidation of firmware code and Linux drivers into a cohesive and unified package

-

Supplying extensive technical documentation covering all aspects comprehensively

-

Development of a Verilog Test Environment with intuitive integration of test cases for comprehensive testing

![]()