Description

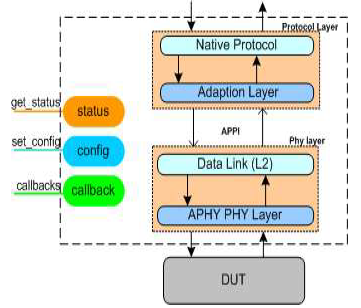

Verifying the MIPI A-PHY is quick and easy with MIPI A-PHY. The Verification IP for MIPI APHY offers the following functionalities and is completely compatible with MIPI A-PHY 1.0 and 1.1 Specification. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support the MIPI A-PHY Verification IP. The optional Smart Visual Protocol Debugger, a GUI-based debugger to speed up debugging, is also included with the MIPI A-PHY Verification IP.

Features

-

Supports MIPI A-PHY specification 1.0 and 1.1.

-

Supports single lane and dual lane, point-to-point and serial communication technology.

-

MIPI A-PHY provides a main unidirectional data stream and a bi-directional low- throughput command and control data stream, and can optionally also deliver the required power supply to peripheral units (i.e., the sensors and/or displays atthe edge of the network) directly via the A-PHY dataline.

-

The model has a rich set of configuration parameters to control MIPI A-PHY functionality.

-

Support multiple speed gears ranging from 2Gbps up to 32 Gbps.

-

Support 5 discrete Downlink Gears: G1, G2, G3, G4, and G5 and Uplink shall be 200Mbps at U1 and U2 gears

-

Support two types of profiles : • Profile 1 (P1-NRZ 8B/10B) • Profile 2 (P2 -PAM 4, 8 ,16)

-

Support clock recovery, Sink Transmitter shall use the recovered Source clock to generate the proper Sink transmit clock, to reach the proper port rate.

-

Support Re transmission request / ACK types.

-

Support Scrambler as per specs.

-

Support two types of Startup Procedure: • Mission Mode, Unidirectional startup

-

Support Wake-Up protocol and below Mode of operation :Non active Mode, Active Mode

-

Implements below PHY layer architecture : • MIPI A-PHY P1 G1/G2 Architecture • RTS By-Pass, 8B/10B PCS, PMD • MIPI A-PHY P2 G1/G2 Architecture • RTS for Uplink and Downlink • 8B/10B PCS,PMD • MIPI A-PHY G3-G5 Architecture • RTS for Uplink and Downlink, 8B/10B PCS for Uplink • PAM 4, 8 ,16 PCS for Downlink, PMD

-

Support below Data Link feature:

-

Link service, Local function,Multi-port function

-

Network function

-

Monitor, Detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

-

Callbacks in transmitter and receiver for various events.

-

MIPI A-PHY Verification IP comes with complete test suite to test every feature of MIPI A-PHY.

Deliverables

-

Complete regression suite containing all the MIPI APHY testcases.

-

Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()