Description

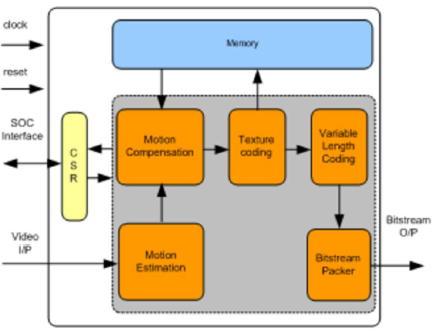

MPEG4 Encoder core is compliant with MPEG-4 standard specification. Through its compatibility, it provides a simple interface to a wide range of lowcost devices MPEG4 Encoder is proven in FPGA environment. The host interface of the MPEG4 can be simple interface or can be AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses.

Features

-

Supports MPEG-4 standard specification.

-

Supports full MPEG-4 encoder functionality.

-

Supports YUV 4:2:2 interleaved data as an input.

-

Supports image width/height as multiple of 16.

-

Supports Half Pel Interpolation (HPI) for motion estimation.

-

Supports generation of streams with resync marker (RM).

-

Supports Unrestricted Motion Vectors (UMV).

-

Supports video resolution up to 1920x1080@60fps.

-

Supports Chroma type 4:4:4, 4:2:2 and 4:2:0.

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices

Benefits

-

Single site license option is provided to companies designing in a single site.

-

Multi sites license option is provided to companies designing in multiple sites.

-

Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

-

Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

Deliverables

-

The MPEG4 Encoder interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes

![]()