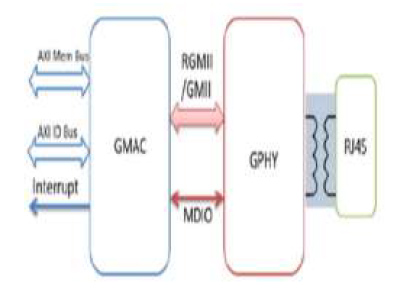

The GPHY is a fully integrated single chip for Gigabit Ethernet applications with lowest power consumption. It is capable of functioning in 10BASE-T, 100BASE-TX, and 1000BASE-T. This GPHY links the GMII-based Media Access Control Layer (MAC) (Giga Media Independent Interface). This GPHY uses either RGMII or GMII to connect to the Media Access Control Layer (MAC). It could support UTP5/UTP3 cable for 10BASE-Te Ethernet or Unshielded Twisted Pair Category 5 Cable (UTP5) for 100BASE-TX Fast Ethernet and 1000BASE-T Giga Ethernet. It includes all of the physical layer functionality of 100BASE-TX described by IEEE802.3u and 1000BASE-T defined by IEEE802.3ab, including the Physical Coding Sub-layer (PCS), Physical Medium Attachment Layer (PMA), and Twisted Pair Physical Medium Dependent Sub-layer (TP-PMD, 100BASE-TX only).

Fully compliant with the IEEE 802.3 / 802.3u/802.3ab10BASE-Te, 100BASE-TX ,1000BASE-T

Interface available to Compliant with TP-PMD standard:ANSI X3.263-1995, Compliant with FDDIPMD standard: ISO/IEC 9314-3: 1990 and ANSIX3.166-1990

Support GMII / RGMII interface to the MAC controller.ï¬Serial management interface compliant with IEEE802.3u (MDIO)

Support Full-Duplex or Half-Duplex Operation,1000BASE Full-Duplex only

Support Auto-Negotiation Next Page /Parallel Detection function compliant with IEEE 802.3u/ab, and Manual configuration is also supported.

Automatic Polarity Correction

Support auto MDI/MDIX crossover function for10BASE-Te / 100BASE-TX

Embedded baseline wander correction (BLW) Circuit

High Performance Digital Clock recovery algorithm

High performance Digital Equalizer for ISI mitigation

High performance Echo / NEXT canceller

Support Wake-On-Lan (WOL) with magic packet

Support efficient energy Ethernet (EEE), Compliant withIEEE802.3az-2010

Support automatic polarity swap

LED Driver for Link, Activity, Duplex, Collision, and Speed Status

Low Power design, with support 803.2az standard-2010(EEE)

Cable diagnostic Test (open/short/cable length)

Working Voltage 3.3/1.8/0.9

Crystal offset +/-300ppm

Silicon Proven in UMC 28nm HPC

Deliverables

Detailed Product Specification Sheet

Verilog Behavioral Model (A) for Simulation Purposes

Liberty Library (db/.lib) for Synthesis, Timing Analysis, and Equivalence Checking

Design for Testability (DFT) using CTL/CTLDB

Standard Test Pattern Generation (ATPG) with SPF (STIL Procedure File)

Layout Exchange Format (LEF) for Automated Place and Route (APR)

Circuit Description Language (CDL) for Layout Versus Schematic (LVS) Verification