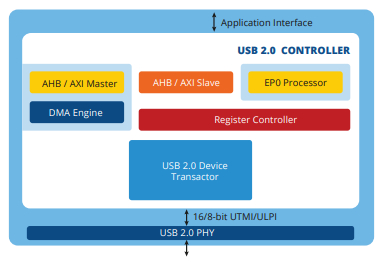

We provide highly configurable USB 2.0 device controller IP Cores. Our host, device, and hub offerings are silicon realized and USB-IF certified by our customers. We provide highly configurable and scalable USB 2.0 device controller IP Core for a wide range of applications. This USB 2.0 device controller is designed for compliance with USB2.0 specification Revision 2.0 and all associated ECN’s. Its physical interface is compliant with ULPI+ or 8/16 bits UTMI PLUS Level3 specification. The system interface is compliant with AHB and/or AXI interface, allowing easy integration. Optional custom bridges can also be bundled as a service offering. The USB 2.0 device controller can optionally include an proprietary high-performance DMA engine for moving USB payloads. The register interface of the DMA Engine is simple and user-friendly, allowing device-side class-specific function drivers to be implemented easily. All licensees can access reference mass storage-class device-side function drivers as well. All buffering associated with the DMA engine is configurable, based on latency and performance requirements. The USB device controller can optionally include an proprietary EP0 processor block for managing all standard requests, directed to the control endpoint – minimizing software development overheads. Class and vendor-specific requests directed to control endpoint are routed to software for processing via the DMA engine.

Optionally, the controller can be provided with no DMA Engine and no buffering, operating in a cut-through mode forwarding and receiving USB payloads and managing only the USB protocol. In this case, the customer can implement their own differentiated DMA engine.

Optionally, a simple transmit and receive buffer is included in this configuration which can be accessed by software over the slave register access interface (typically AHB). This option results in very low-footprint hardware, useful for scenarios where the software can completely manage USB traffic including sequencing of the USB transactions.

Flexible RTL Implementation

HDL Test Bench with Behavioral Models

Test Case Catalog

Protocol Compliance Validators, Bus Observers, and Performance Analyzers

Configurable Synthesis Framework

Design Reference Handbook

Verification Guidebook

Synthesis Procedure Manual

FPGA Validation Platform for Pre-Tape-out Verification

Firmware Reference Implementation and Documentation