Description

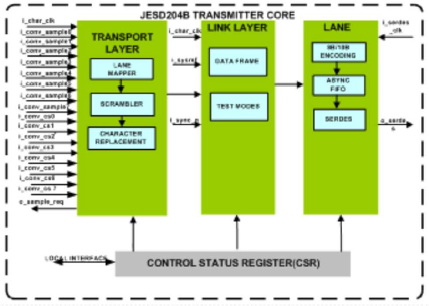

The JESD204B interface offers complete support for the synchronous serial JESD204B interface, which is compliant with the JESD204B.01 version standard. It offers a user-friendly interface to a variety of inexpensive devices due to its interoperability. In an FPGA context, the JESD204B Transmitter IIP has been tested. The JESD204B's host interface options include a basic interface, an AHB, AHB-Lite, an APB, an AXI, an AXILite, a Tilelink, an OCP, a VCI, an Avalon, a PLB, a Wishbone, or a custom protocol. Verilog and VHDL both have native support for JESD204B Transmitter IIP.

Features

-

Compliant with JESD204 specification JESD204A, JESD204B.01.

-

Full JESD204B transmit functionality.

-

Supports data rate upto 12.5 Gbps.

-

Supports programmable clock frequency up to 12.5 GHz.

-

Supports up to Subclass 0, 1, 2.

-

Supports up to Version A and B.

-

Supports 1 to 8 lanes.

-

Supports 1 to 8 converters per transmitter.

-

Supports frame sizes of 1,2,4,8 and 16 octets per frame.

-

Supports HD-mode.

-

Supports 1 to 32 bit data width per converter.

-

Supports CF = 0 and 1 control words per frame clock period per link.

-

Supports 0 to 3 control bits per sample.

-

Supports 1 to 8 samples per converter.

-

Supports 1 to 32 frames per multiframe.

-

Supports 4, 8, 12, 16, 20, 24, 28 and 32 bits per sample.

-

Supports 0 to 15 bank ID – extension to DID.

-

Supports 0 to 255 device identification number.

-

Supports 0 to 7 lane identification number.

-

Supports different Serdes interfaces 10,20,40,60 bits and custom bits per lane.

-

Continuous sequence of a scrambled jitter pattern (JSPAT) and modified random pattern (modified RPAT).

-

Continuous sequence of either /D21.5/ or /K28.5/ characters for code group synchronization.

-

Repeated transmission of a lane alignment sequence, preceded by a code group synchronization sequence.

-

Scrambler can be enabled or disabled.

-

Supports 8b/10b encoding.

-

MCDA-ML (Multiple-Converter Device Alignment, Multiple-Lanes) device supported.

Deliverables

-

The JESD204B Transmitter interface is available in Source and netlist products.

-

The Source product is delivered in verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases.

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files.

-

IP-XACT RDL generated address map.

-

Firmware code and Linux driver package.

-

Documentation contains User's Guide and Release notes.

![]()