Description

MIPI UniPro Verification IP is compliant with MIPI UNIPRO specification and verifies UNIPRO devices. Experts that have previously worked on difficult protocols have created the UNIPRO Verification IP. Our MIPI Unipro Verification IP has been validated with several clients. MIPI UniPro Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env MIPI UniPro Verification IP comes with optional Smart Visual Protocol Debugger which is GUI based debugger to speed up debugging.

Features

-

Supports MIPI UniPro specification 1.41,1.6,1.8 and 2.0.

-

Support MIPI MPHY specification 3.0,4.1 and 5.0.

-

Supports multiple connections in L4 Layer segments.

-

Supports C port arbitration at both segment level and packet level with buffer based E2E checking.

-

Supports Layer 3 error injection and detection.

-

Supports L2 data frames and control frames.

-

Phy layer supports MPHY serial, MPHY RMMI (10,20,40 bit) Interface.

-

Support error injection of all PACP frames.

-

Supports M-PHY phyiscal layer support with RMMI

-

Supports Scrambler, SKIP insertion and Marker 2 extension.

-

Suports both data link layer frames • Data Frames, Control Frames PHY layer features • Transmission and reception of encoded PHY symbols. • Transmission of PHY IDLE symbols when no data is supplied. • Method to re-initialize the forward Link to overcome error situations. • Provision of different power modes and a method to signal them from transmitter to receiver.

-

PHY adapter layer features • Transmission and reception of Data Link layer control and data symbols via underlying PHY. • Lane distribution and merging in multi-lane ports. • Support various kind of errors injects in LSS, PA Layer for various operation.

-

Transport layer features

-

Data Link and Network layer features

-

Monitor,Detects and notifies the testbench of all protocol and timing errors.

-

Supported below latest Version 2.0 features • Supports HS-G5 gear in HS mode and PWM G1 gear alone supported, remaining PWM gears are removed • Supports Linkstartup sequence start either HS Mode(HS G1A or HS G1B) or LS mode(PWM G1)

-

Supports RMMI bus width extended to 80bits and 160 bits per lane interface in PHY Layer

-

Supports complete DME functionality.

-

Supports all layer error injection and detection.

-

Monitor, Detects and notifies the testbench of all protocol and timing errors.

Deliverables

-

Complete regression suite containing all the MIPI UniPro testcases.

-

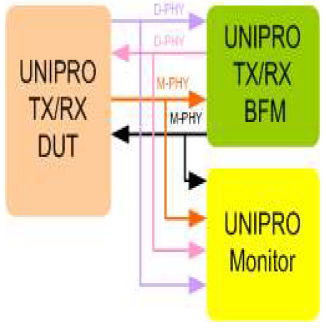

Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()