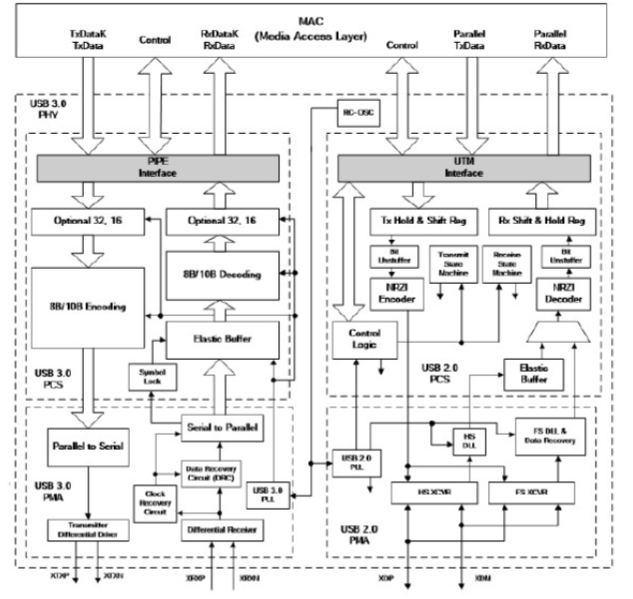

A Universal Serial Bus (USB) transceiver which is provided for peripheral devices. The PHY is compliant with the USB 3.0 (USB SuperSpeed), USB 2.0 PIPE and UTMI specifications. The USB3.0 PHY IP transceiver is optimized for low power consumption and minimal die area without sacrificing performance and high data throughput. The USB3.0 PHY IP comprises a complete on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, built-in self-test module with embedded jitter injection, and a dynamic equalization circuit that ensures full support for high-performance designs. Standard PHY interface (PIPE) enables multiple IP sources for USB3 MAC layer. Allowable analog circuit parameter adjustment and internal test control Built-in Self-Test with embedded Jitter Injection Output Jitter reduction with constant power technique.

Deliverables

Layout Data in GDSII Format with Layer Details .

LEF Files with Placement and Routing Views

Timing and Power Model Repository in .lib Format

Verilog Representation of Circuit Behavior

Netlist Annotated with Standard Delay Format Timing

Application Notes Providing Layout Insights

LVS and DRC Verification Results