Description

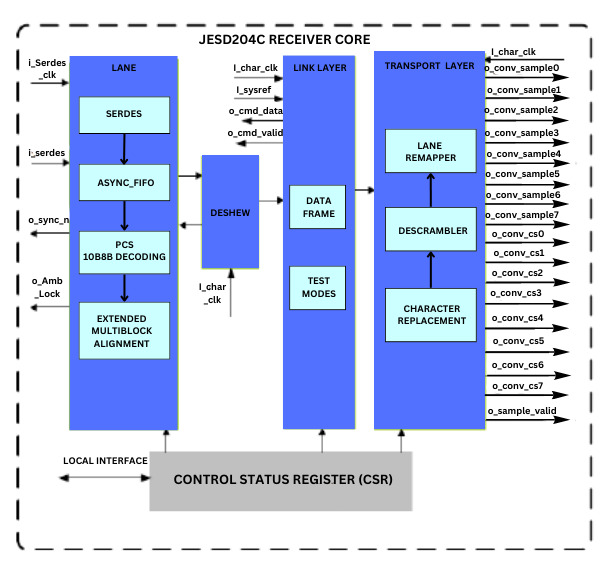

The JESD204C Receiver IP Core is full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The JESD204C Receiver IP can be implemented in any technology. The JESD204C Receiver IP core supports the JESD204C standard. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHBLite, APB,AXI,AXI Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses. The JESD204C Receiver IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The JESD204C Receiver IP is validated in using FPGA. The Receiver core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Compliant with JESD204 specification JESD204A, JESD204B.01 and JESD204C

-

Full JESD204C receive functionality

-

Supports data rate upto 32 Gbps

-

Supports programmable clock frequency up to 32 GHz

-

Supports up to Subclass 0, 1, 2 Supports up to Version A, B and C

-

Supports 1 to 8 lanes

-

Supports 1 to 8 converters per receiver

-

Supports frame sizes of 1,2,4,8 and 16 octets per frame

-

Supports HD-mode

-

Supports 1 to 32 bit data width per converter

-

Supports CF = 0 and 1 control words per frame clock period per link

-

Supports 0 to 3 control bits per sample Supports 1 to 8 samples per converter

-

Supports 1 to 32 frames per multiframe

-

Supports 4, 8, 12, 16, 20, 24, 28 and 32 bits per sample

-

Supports 0 to 15 bank ID – extension to DID

-

Supports 0 to 255 device identification number

-

Supports 0 to 7 lane identification number

-

Supports 10/8b decoding Supports 66b/64b decoding Supports 80b/64b decoding

-

Supports Forward Error Correction (FEC) and cyclic redundancy checks (CRC)

-

Supports single block, Multi block and extended multi block

-

Supports reporting of various error statistics

-

Supports different Serdes interfaces 10, 20, 40,60 bits and custom bits per lane

-

Scrambler can be enabled or disabled

-

MCDA-ML (Multiple-Converter Device Alignment, Multiple-Lanes) device supported

Deliverables

-

RTL design in Verilog

-

Lint, CDC synthesis script with waiver files

-

Lint, CDC synthesis reports

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Technical documentation in greater detail

-

Easy to use Verilog test environment with Verilog test cases

![]()