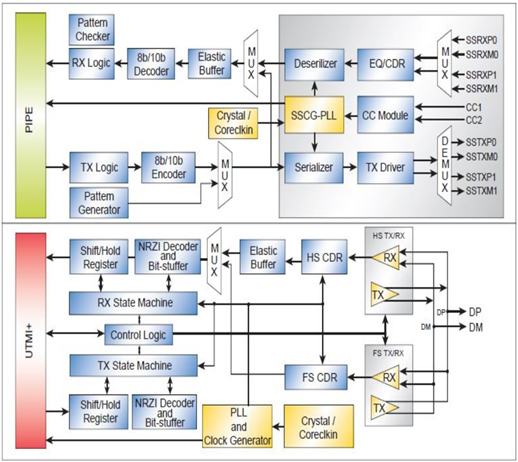

All USB 3.2 Gen2X1 host and peripheral applications are supported up to 10Gbps by the USB 3.2 Gen2X1 transceiver IP. It complies with UTMI+ and PIPE4.0 requirements. The USB 3.2 Gen2X1 IP is backward compatible with high-speed data rates of 480Mbps, full-speed data rates of 12Mbps, and low-speed data rates of 1.5Mbps and incorporates high-speed mixed signal circuits to permit Gen2 and Gen1 traffic. In order to support the USB Type-C connector, the USB 3.2 Gen2X1 IP includes an active switch to enable bi-directional plug-in and specific functionality (such as VBUS setup and USB attachment cable orientation detection) through the CC1/CC2 pins defined in the Type-C connection.

Deliverables

Graphic Data System II Format with Layer Mapping

Layout Exchange Format for Placement and Routing Views

Liberty Format for Timing and Power Models

Verilog Representation of Functional Behavior

Netlist with Timing Annotations in SDF

Recommended Practices and Design Notes for Layout

Verification Reports for LVS and DRC Compliance