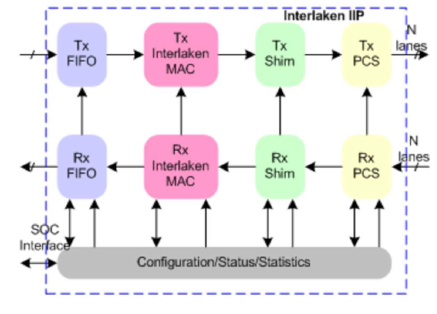

Description

Interlaken interface provides full support for the Interlaken synchronous serial interface, compatible with Interlaken version 1.2 specification. Through its Interlaken compatibility, it provides a simple interface to a wide range of low-cost devices. Interlaken IP is proven in FPGA environment. The host interface of the Interlaken can be simple interface or can be AMBA APB, AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

Features

-

Compliant with Interlaken protocol specification v1.2

-

Interlaken look as side protocol 1.1

-

Interlaken retransmission extension specification 1.2

-

Interlaken Reed-Solomon Forward Error Correction Extension 1.1

-

Interlaken Interoperability Recommendations 1.11

-

Interlaken Dual Calendar Extension 1.0

-

Supports up to 1000Gbps

-

Supports single channel and multichannel (up to 4 channel)

-

Supports for 256 communications channels, or up to 64K with channel extension

-

Supports configurable number of lanes from 1 to 64 lanes

-

Supports configurable burst max, burst short and metaframe length.

-

Supports the In-bound/out-bound flow control

-

Supports burst interleaved and Packet mode

-

Supports 80,64,40,32, 20,16,10 and 8 bit per lane Serdes interface

-

Supports 64/67 encoding and decoding with DC balance

-

Supports automatic word and lane alignment

-

Supports self-synchronizing data scrambler

-

Supports status messaging

-

Supports ILA overhead insertion and extraction

-

Supports CRC32 generation and checking for lane data integrity

-

Supports transmit and receive clock and data rate decoupling with programmable asynchronous FIFO

-

Supports unidirectional and bidirectional operation

-

Supports lane protection

-

Supports test pattern generation and checker

-

A simple control word structure to delineate packets, similar in function to SPI4.2

-

Optional support for scheduling enhancement to avoid unused bandwidth by using decision algorithm

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices.

Deliverables

-

Availability of the Interlaken interface in Source and netlist formats.

-

Delivery of the Source product in plain text Verilog, with the option for VHDL or SystemC code if required.

-

Provision of an intuitive Verilog Test Environment accompanied by Verilog Testcases for ease of use.

-

Inclusion of Lint, CDC, Synthesis, and Simulation Scripts along with waiver files.

-

Generation of an address map using IP-XACT RDL.

-

Packaging of firmware code and Linux drivers into a single bundle.

-

Documentation comprising a User's Guide and Release notes.

![]()