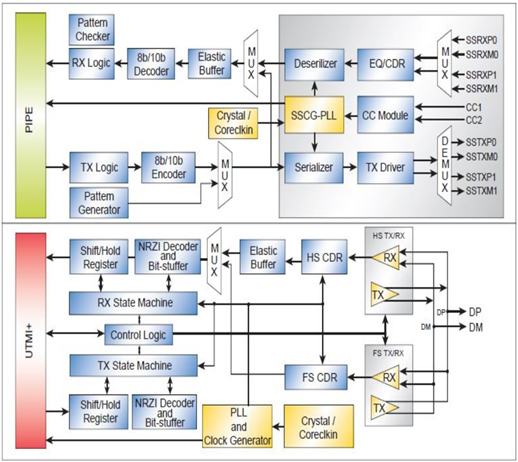

The USB 3.2 Gen2X1 transceiver IP offers all USB 3.2 Gen2X1 host and peripheral applications up to 10Gbps. Both the UTMI+ and PIPE4.0 specifications are met by it. The USB 3.2 Gen2X1 IP includes high-speed mixed signal circuits to enable Gen2 and Gen1 traffic and is backward compatible to high-speed data rates at 480Mbps, full-speed data rates at 12Mbps, and low-speed data rates at 1.5Mbps. The USB 3.2 Gen2X1 IP incorporates an active switch to support bi-directional plug-in and particular functionalities (such as VBUS configuration and USB attachment cable orientation detection) through the CC1/CC2 pins specified in the Type-C connection in order to support the USB Type-C connector.

Deliverables

Integrated Circuit Layout and Layer Map in GDS2

LEF Representation of Placement and Routing

Standard Cell Characterization Library

Behavioral Description in Verilog

Circuit Connectivity and Timing Constraints in SDF Format

Design Rules and Application Guidelines for Layout Layout

Versus Schematic and Design Rule Check Validation Reports