Description

The capabilities of CSI-2 are enhanced by MIPI CSI-3, a new generation of camera serial interface. In comparison to CSI-2, CSI-3 uses fewer pins while offering more bandwidth thanks to the use of a multipurpose connection based on a single protocol stack (UniPort-M). The camera serial Interface 3 version 1.2 MIPI Alliance specification is completely supported by the MIPI CSI-3 Verification IP, which offers the functionality listed below. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and nonstandard verification environments all natively support the MIPI CSI-3 Verification IP. The optional Smart Visual Protocol Debugger, a GUI-based debugger that speeds up debugging, is included with the MIPI CSI-3 Verification IP as well.

Features

-

Supports Version 1.2 MIPI CSI-3 Specification

-

Supports transmission of Image frame

-

Supports transmission of Attribute packets

-

Supports Data transmission on multiple Virtual Channels

-

CAL provides support for camera configuration, camera control and data transport

-

Includes Proven MIPI UniPro and M-PHY bfm components for lower layer verification

-

M-PHY supports various transmission speed steps and ranges from 0.01 Mbps up to 5.8 Gbps per Lane

-

Supports all lane configuration

-

Supports implementation of standalone ISPs

-

Supports interleave the streams

-

Supports all CSI-2 legacy data formats

-

Supports following error insertion and detection

-

All MIPI MPHY errors, Disparity errors, Invalid code group errors, All Unipro errors, Invalid frame formats, L2 Credit violation, Cport buffer violation

-

All LSS errors, No response error injection

-

CRC errors, Reserve field error injection

-

Over and undersize errors, Lane mapping and disconnection error, All CSI-3 erros, Data type errors

-

Over and undersize errors, Malformed packet errors

-

Attribute errors

-

Supports compressed image data

-

The CCI device supports all four different read operations • Single read from random location • Sequential read from random location • Single read from current location • Sequential read from current location

-

The CCI device supports all two different write operations • Single write to random location • Sequential write starting from random location

-

The CCI supports the following register width

-

8-bit, 16 bit, 32 bit, 64 bit

-

Monitor, Detects and notifies the testbench of all protocol and timing errors

-

Supports constraints Randomization

-

Status counters for various events in bus

-

Callbacks in transmitter and receiver for various events

-

MIPI CSI-3 Verification IP comes with complete test suite to test every feature of MIPI CSI-3 Version 1.0 specification.

-

Functional coverage for complete MIPI CSI-3 features

Deliverables

-

Complete regression suite containing all the MIPI CSI-3 testcases.

-

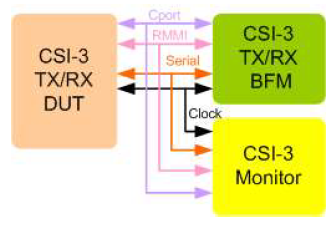

Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()