Description

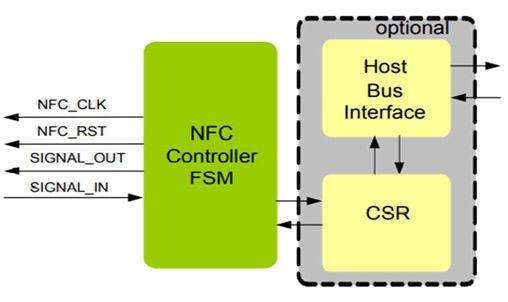

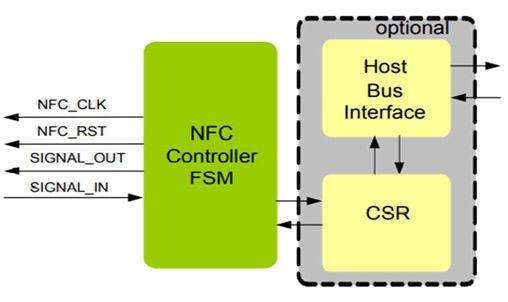

The NFC Controller IP Core is full-featured, easy-touse, synthesizable design that is easily integrated into any SOC or FPGA development. The NFC Controller IP can be implemented in any technology. The NFC Controller IP core supports the ISO provides the following features ISO/IEC 18092, ISO/IEC 14443, ISO/IEC 15693 and ECMA 340 Specifications. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses. The NFC Controller IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The NFC Controller IP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Implemented in Unencrypted Verilog, VHDL and SystemC

-

Compliant with NFC Specification ISO/IEC 18092, ISO/IEC 14443, ISO/IEC 15693 and ECMA 340 standards.

-

Complete NFC Controller PCD/PICC functionality.

-

Support Half Duplex of operations.

-

Supports all the four data rates.

-

106 kbps

-

212 kbps

-

424 kbps

-

848 kbps

-

Supports two different kinds of communication modes.

-

Active communication mode

-

Passive communication mode

-

Support both Type A and Type B.

-

Supports the Multi Activation feature, which allows the Initiator to hold several Targets active simultaneously.

-

Supports the chaining feature, which allows the Initiator or Target to transmit information that does not fit in a single block, by dividing the information into several blocks.

-

Supports Configurable timing functions.

-

Guard time

-

Frame delay time

-

Frame Waiting time

-

Waiting Time extension

-

Supports the following types of error detection.

-

Sync error

-

DID error

-

Length error

-

Acknowledgement error

-

Invalid command error

-

CRC error

-

Parity error

-

Re-transmission of corrupted messages.

-

Supports to change the parameters (Transfer speed and Frame length) of PCD and PICC after the activation.

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to

-

Microprocessor/Microcontroller devices

Deliverables

-

RTL design in Verilog

-

Lint, CDC, Synthesis Scripts with waiver files

-

Lint, CDC, Synthesis Reports

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Technical documentation in greater detail

-

Easy to use Verilog Test Environment with verilog testcases