Description

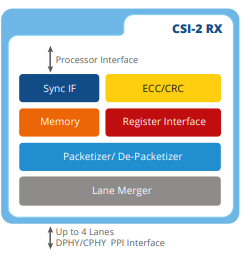

The MIPI Camera Serial Interface 2 (CSI-2) is an interface between a Camera and a host processor baseband application engine. This interface is defined by MIPI Alliance, which defines a series of modules in a MIPI compliant product. This MIPI CSI-2 Receiver is used in mobile and high–speed serial applications as a controller for receiving camera video and transmitting camera commands from/to MIPI CSI-2 Transmitter over MIPI lines. The camera data is encoded and then transmitted. The MIPI CSI-2 Transmitter along with our MIPI CSI-2 Receiver and MIPI DPHY provides a complete solution for decoding MIPI CSI-2 data.

Features

-

Compliant with MIPI CSI-2 Specification v1.3

-

Complaint with MIPI DPHY V1.2

-

Compliant with MIPI CPHY V1.1

-

Lane configuration: CSI2_ RX: Programmable 1, 2, or 4 Data Lane Configuration.

-

Operate in continuous and non-continuous clock modes.

-

Supported YUV Data Types : YUV420_8bit, YUV420_10bit, YUV422_8Bit, YUV422_10bit, YUV420_8Bit_CSPS, YUV420_10bit_CSPS, LEGACY YUV420_8bit

-

Supported RGB Data Types: RGB888, RGB565, RGB666, RGB555, and RGB444.

-

Supported RAW Data Types: RAW6, RAW7, RAW8, RAW10, RAW12, and RAW14.

-

Supports User defined data types.

-

Pixel Interface: 64 bit Pixel data alignment

-

Data Rate: CSI-2 DPHY : Up to 1.5 Gbps per lane

-

Selectable Register configurations through Generic Parallel interface.

Deliverables

-

Configurable RTL Code

-

HDL-based test bench and behavioral models

-

Test cases

-

Protocol checkers, bus watchers, and performance monitors

-

Configurable synthesis shell

-

Documentation

-

Design guide

-

Verification guide

-

Synthesis guide

Benefits

-

Data lane count

-

Color modes

-

Pixel interface width

-

Application interface –Pixel or AXI

-

Command FIFO depth

-

Highly modular and configurable design

-

Layered architecture

-

Active low async reset

-

Clearly demarcated clock domains

-

Extensive clock gating support

Applications

-

Mobile

-

IOT

-

Automotive

-

Wearables

![]()