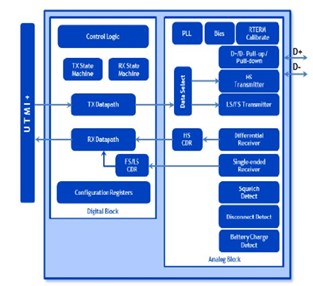

The whole physical layer (PHY) IP solution for USB 2.0 was designed for outstanding performance and low power consumption. The High-Speed USB 2.0 Transceiver is implemented by the USB2.0 IP and can be utilized with hosts, devices, or OTG function controllers. The USB2.0 PHY IP, which supports Full-Speed (12 Mbps) and Low-Speed (1.5 Mbps) data rates, is the specification that comes after UTMI+level 3.High-speed data transfer @ 480Mbps can be achieved by combining several mixed-signal circuits. Additionally supported by the USB2.0 PHY IP are the enhanced USB Battery Charging standards, which are designed for use in consumer electronics and mobile devices. Numerous factories and nodes, including "TSMC 28HPC+, TSMC 40LP, TSMC 40LL, UMC 28HPC, UMC 40LP, UMC 55SP, UMC 55EF, SMIC 14SF+, SMIC 40LL, SMIC 55LL," implement the USB 2.0 PHY IP standard. Performance and data throughput were unaffected by the tiny chip size and low power consumption of the USB2.0 PHY IP ransceiver. The USB2.0 PHY IP offers a full on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, a clock generating block provided by an internal PLL, and a resistor termination calibration circuit in order to fully enable host and device functionality.

Compliant with USB2.0 and USB1.1 specification

Compliant with UTMI Specification Version level 3.

Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

16-bit, 30MHz or 8-bit, 60MHz parallel interface for HS/FS

Serializing for transmitting data stream and Deserializing for receiving data stream

USB Data Recovery and Clock Recovery on receiving

Integrated Bit Stuffing and NRZI encoding for Transmit

Integrated Bit Un-Stuffing and NRZI decoding for Receive

SYNC and EOP generation on transmit packets and detection on receive packets

Internal reference resistor that replaces the external reference resistor

Built in self test for production testing

Supports USB suspend state and remote wakeup

Supports detection of USB reset, suspend and resume signaling

Supports high speed identification and detection as defined by USB 2.0 Specification

Support high speed host disconnection detection

Silicon Proven in TSMC 28nm, TSMC 40nm, UMC 28nm, UMC 40nm, UMC 55nm, SMIC 14nm, SMIC 40nm, SMIC 55nm

Silicon Proven in TSMC 12FFC.

Deliverables

GDSII Format with Layer Assignment Details

Views of Placement and Routing in .LEF File Format

Standard Cell Library with Timing and Power Information

Behavioral Model Expressed in Verilog Syntax

Netlist Including Timing Annotations in SDF Format

Recommendations for Effective Layout Design and Execution

Validation Reports Ensuring Layout Adherence to Schematic and Rules