Description

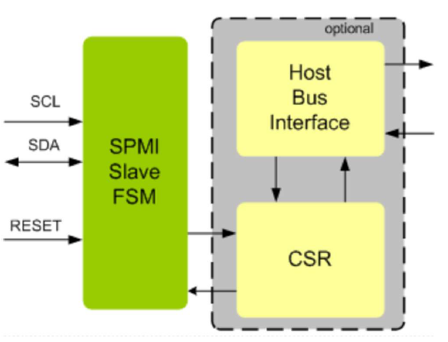

MIPI SPMI Slave interface provides full support for the two-wire MIPI SPMI synchronous serial interface, compatible with SPMI specification. Through its SPMI compatibility, it provides a simple interface to a wide range of low-cost devices. MIPI SPMI Slave IP is proven in FPGA environment.The host interface of the MIPI SPMI can be simple interface or can be AMBA APB, AMBA AHB, AMBA AHB-Lite, AMBA AXI, AMBA AXI-Lite, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

Features

-

Supports 2.0 and 1.0 MIPI SPMI Specification

-

Full MIPI SPMI Slave functionality

-

Supports following frames • Command Frame • Data/Address Frame • No Response Frame

-

Supports ACK/NACK as per 2.0 specs

-

Support for slave requests through Alert(A) / Slave Request (SR) bit.

-

Support for slave request hold.

-

Glitch suppression (optional).

-

Supports extended register read/writes

-

Supports wakeup command

-

Supports Authentication Command Sequence

-

Device Descriptor Block Command Sequences

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to microprocessor/microcontroller devices.

Benefits

-

Single Site license option is provided to companies designing in a single site.

-

Multi Sites license option is provided to companies designing in multiple sites.

-

Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

-

Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

Deliverables

-

The MIPI SPMI Slave interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()