Description

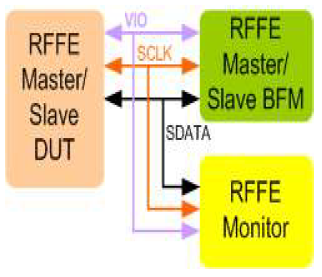

The MIPI RFFE bi-directional two-wire bus may be intelligently verified using the MIPI RFFE Verification IP. The MIPI RFFE Verification IP offers the following functionalities and is completely compatible with the MIPI Alliance specification for RF Front-End Control Interface versions 1.0, 2.0, 2.1, and 3.0. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support the MIPI RFFE Verification IP. To expedite debugging, the MIPI RFFE Verification IP offers an optional Smart Visual Protocol Debugger, a GUI-based debugger.

Features

-

Full MIPI RFFE Master and Slave functionality.

-

Operates as a Master, Slave, or both.

-

Monitor, Detects and notifies the testbench of all protocol and timing errors.

-

Supports all topologies as per the MIPI RFFE specification.

-

Supports following frames. • Command Frame • Data/Address Frame • No Response Frame • Bus ownership transfer • Interrupt polling • Master write and read • Master context write and context read

-

Various kind of Master and Slave errors generation. • Undefined command frame • Command frame with parity, length error • Address frame with parity error • Data frame with parity error • Read and Write of unused register • Read using the broadcast ID or a GSID • Various errors in Bus ownership transfer

-

Glitch monitor and injection. • Support injection of glitch at all positions of SDATA and SCLK • Supports detection of glitches

-

Supports interrupt summary and identification command sequence.

-

Supports Master ownership handover.

-

Support Master write and read sequence.

-

Support Trigger and Extended trigger modes.

-

Support Masked write command sequence.

-

Support Silent Master initiated bus park.

-

Support Interrupt capable slave.

-

Support Synchronous read.

-

Support Normal and Secondary operation mode.

-

Support USID Programming Procedure 1,2 and 3.

-

Support Group slave ID, Low power testing

-

Support Timed Trigger and Mappable Trigger.

-

Support Bus Clocked Condition.

-

Supports device enumeration.

-

Bus-accurate timing, Supports half speed.

-

Callbacks in master, slave and monitor for variousevents.

-

Status counters for various events in bus.

-

Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

Deliverables

-

Complete regression suite containing all the MIPI RFFE testcases.

-

Examples showing how to connect various components, and usage of Master, Slave and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()