Description

This DDR (Double Data Rate) PHY IP supports DDR3/DDR3L/DDR4, provides low latency, and enables up to 1600Mbps throughput. The PHY IP is silicon proven and designed for ease of integration and faster time-to market. The DDR IP is compliant with the latest JEDEC standards and is silicon proven.

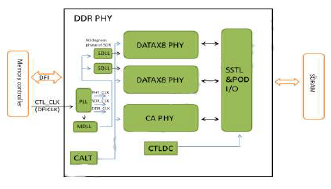

The DDR PHY is interface between DDR controller and SDRAM. The DDR controller is used to control DRAM devices as well as to access the data stored on these devices. Provide multiple AXI interface for AXI master and support DFI standard for DDR PHY to support DDR4/3, data rate 1600Mbps, X8/X16, four ranks, Write leveling, Data training, low power mode and standby mode. The DDR PHY is used to control DRAM devices to access the data stored in these devices, provide SSTL135, POD12 and LVSTL interfaces for DDR3L, DDR4 and DDR3.

Optimized for high performance, low latency, low area, low power, and ease of integration, the DDR4, DDR3, DDR3L PHY is provided as a hard DDR PHY that is primarily delivered as GDSII including integrated application-specific DDR4, DDR3, DDR3L I/Os. Supporting the GDSII-based PHY is the RTL-based PHY. The DDR4, DDR3, DDR3L PHY includes a DFI 4.0 interface to the memory controller and can be combined controllers for a complete DDR interface solution.

Features

-

Supported DRAM type: DDR3/DDR3L/DDR4

-

Maximum controller clock frequency of 400MHz resulting in maximum DRAM data rate of 1600Mbps

-

Interface: SSTL15/SSTL135/POD12

-

Data path width scales in 16-bit increment

-

Four module for flexible configuration: CA/DQ_X16/DQ_X8/ZQ

-

Programmable output impedance(DS)

-

Programmable on-die termination(ODT)

-

Core power:0.9V, I/O power(VDDQ):1.5V/1.35V/1.2V, RX power:1.8V

-

ESD : 2KV/HBM, 200V/MM, 500V/CDM

-

Support ZQ calibration

-

Support 4 ranks by each CA module

-

Support write-leveling, CBT

-

Support PHY internal VREFDQ auto decision

-

Per-bit deskew in read and write datapath

Deliverable

-

User Manual

-

Behavior model, and protected RTL codes

-

Protected Post layout netlist and

-

Standard Delay Format (SDF)

-

Synopsys library (LIB)

-

Frame view (LEF)

-

Metal GDS (GDSII)

-

Test patterns and Test Documentation

-

Verilog HDL

Benefits

-

PHY functionality is verified in NC-Verilog simulation software using test bench written in Verilog HDL

-

Low Power

-

Low Area

-

Low Latency

-

JEDEC, the standards body responsible for memory standards has defined and developed DRAM categories such as DDR: DDR, DDR2/3/4 mobile DDR: LPDDR2/3/4 high bandwidth DRAM: HBM, HBM2/2E/3)

Applications

-

SSD Controllers

-

Automotive

-

Application Processors

-

Digital Baseband Modems

-

Set-Top-Box

-

Digital TV

-

OTT

-

Surveillance

-

Multimedia

-

IOT

-

Setup Box

-

Survelliance

-

Storage

![]()