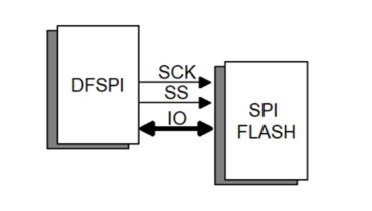

The FSPI is a fully configurable SINGLE, DUAL, QUAD and OCTAL SPI master/slave device, which allows user to configure polarity and phase of serial clock signal (SCK). The FSPI system is flexible enough to interface directly with numerous standard product peripherals from several manufacturers. It supports two DMA modes: single transfer and multitransfer. These modes allow FSPI to interface to higher performance DMA units, which can interleave their transfers between CPU cycles or execute multiple byte transfers. FSPI is fully customizable, which means it is delivered in the exact configuration that meets users’ requirements.

Set of software accessible control registers to

execute any Flash memory command

Support for most popular SPI like FLASH memories and PSRAM

Supports any device clock frequency, polarity and phase

Programmable baud rate generator

Built in FLASH Commands decoder supports most popular FLASH devices

Optional built in AES Encoder/Decoder

DMA support

Built in support for Hyper Bus TM standard

Optional (added on special request) support for other standards: xSPI and XccelaTM

Compliant with latest AMBA Specification, supports APB, AHB, AXI bus interfaces

Single, Dual, Quad and OCTAL SPI transfer/reception

Execute in place – XIP functionality support

Data Bus Size configuration to 8, 16 or 32 bits wide

Optional FIFO size extension

Maximum supported Flash address range - 32 bits

Up to 4 SPI slaves can be addressed

Software Slave Select Output – SSO - selection

Automatic Slave Select outputs assertion

System error detection

Interrupt generation

Bit rates generated as 1/ 2 1/255 of system clock.

Four SPI transfer formats supported: CPOL/CPHA.

Simple interface allows easy connection to microcontrollers

Fully synthesizable, static synchronous design with no internal tri-states

Deliverables

EDIF Netlist, VHDL or Verilog Source Code

VHDL or VERILOG test bench environment

Technical documentation

Installation Notes

DoxyGen software driver documentation

Linux Driver – Optional

Synthesis scripts

Technical support

IP Core Implementation Support and 3 months of maintenance.