Description

A SOC or ASIC's USB 1.0/1.1/2.0 component may be intelligently verified using the USB 1.0/1.1/2.0 Verification IP. It offers backwards compatibility support for previous USB standard versions 1.0, 1.1, and 2.0. Different speeds can be used for data transfer via USB 1.0, 1.1, and 2.0 VIP. Of which high speed (480 Mbit/s), full speed (12 Mbit/s), or low speed (1.5 Mbit/s) logically implies. It executes all conceivable protocol tests in a guided or highly randomized manner, adding the potential to build a large range of situations to successfully validate the DUT. In this manner, the whole protocol violation is detected. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support USB 1.0/1.1/2.0 Verification IP. Verification IP for USB 1.0, 1.1, and 2.0

Features

-

Compatible with USB 1.0, 1.1 and USB 2.0 specification

-

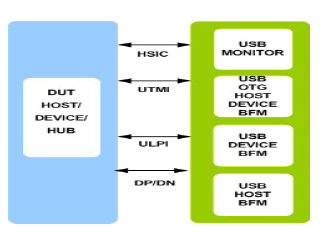

Supports Standard USB 2.0 interface, UTMI, UTMI+, ULPI and HSIC interfaces.

-

Standard DP/DM bus interface is supported.

-

Supports Link Power Management (LPM).

-

Supports constrained randomization of protocol attributes.

-

All USB2.0 transfer types (Control, Isochronous, Interrupt, Bulk) are supported.

-

Supports both transaction level (Setup, In, Out, Ping) and packet level (Token, Data, Handshake, SOF) transmission/reception.

-

Supports SRP and HNP compliance checking.

-

Provides SOF generation support.

-

Programmable inter packet and end-to-end delays.

-

Proficiency to generate random packets/transactions and respond to packets/transactions in directed or randomized fashion.

-

Combination of OTG device communication

-

OTG device to Embedded Host

-

Targeted Host to peripheral only B-device

-

OTG device to OTG device

-

Supported devices, Dual A, B device, Embedded host SRP only B device

-

Supported protocols SRP, HNP, HNP polling

-

Suspend/Resume/Remote wakeup

-

ADP

-

Supported speeds HS and FS

-

Supported feature selector

-

b_hnp_enable

-

a_hnp_support

-

a_alt_hnp_support

-

Support the all timeout condition

-

a_wait_vrise_tmout,

-

a_wait_vfall_tmout

-

a_wait_bcon_tmout, a_aidl_bdis_tmout

-

a_bidl_adis_tmout

-

Supports all types of error injection and detection. Errors include:

-

Corrupt Sync, PID, CRC-5, CRC-16, Corrupt Endpoint Address Byte

-

Corrupt Setup Payload Size

-

Corrupt Setup Stage Data Payload

-

Corrupt EOP byte, Bit stuffing error

Deliverables

-

Complete regression suite containing all the USB 1.0/1.1/2.0 testcases.

-

Examples showing how to connect various components, and usage of BFM and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation also contains User's Guide and Release notes.

![]()