Description

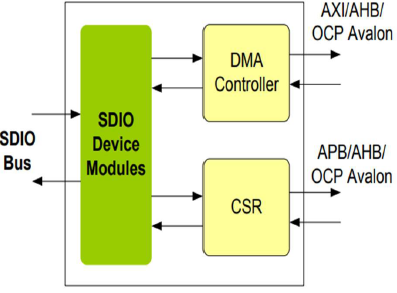

The SDIO Device Controller IP Core is full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The SDIO Device Controller IP can be implemented in any technology. The SDIO Device Controller IP core supports the Part 1 Physical Layer Specification Version 3.01 and SD specification Part E1 SDIO version 3.00. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, APB, OCP, VCI, Avalon PLB, Wishbone or custom buses. The SDIO Device Controller IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The SDIO Device Controller IP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Compliant with Part 1 Physical Layer Specification Version 3.01 and earlier versions

-

Compliant with Part E1 SD Specification version 3.00 and earlier versions

-

Supports all commands/response types

-

Supports 1-bit, 4-bit, 8 bit SD bus mode and SPI Bus mode

-

Supports CRC7 checking/generation for command/response Supports CRC16 checking/generation for data transfer

-

Supports default and high speed modes

-

Supports SDR12, SDR25, DDR50, SDR 50 and SDR104 modes

-

Supports single byte, single block and multiple block transfer operations

-

Supports read-write and read-only cards

-

Supports different memory capacities given below, • Standard Capacity SD Memory Card (SDSC): Up to 2 GB • High Capacity SD Memory Card (SDHC): More than 2GB and up to 32GB • Extended Capacity SD Memory Card (SDXC): More than 32GB and up to and including 2TB

-

Supports switch function command

-

Supports block count setting (CMD23) command

-

Supports direct commands during data transfer

-

Supports multiple IO functions and one memory

-

Supports Asynchronous Interrupt to Host Controller

-

Supports Suspend and Resume operation

-

Supports Read Wait control operation

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to microprocessor/microcontroller devices

Deliverables

-

RTL design in Verilog

-

Lint, CDC, Synthesis Script with waiver files

-

Lint, CDC, Synthesis Reports

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Technical documentation in greater detail

-

Easy to use Verilog Test Environment with Verilog Test cases

![]()