Description

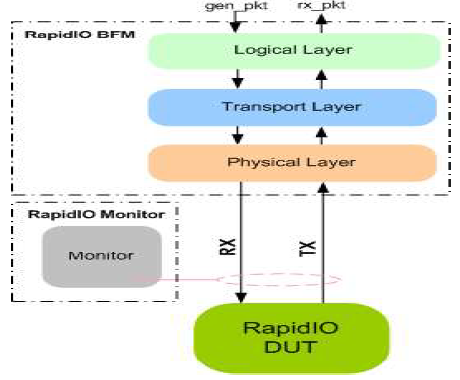

An intelligent method for verifying the RapidIO bi-directional two-wire bus is provided by Rapid IO Verification IP. Versions 4.1 and earlier of the RapidIO Interconnect Specification are compatible with the RapidIO Verification IP. A physical layer, a transport layer, and a logical layer are the three main implementation layers of RapidIO VIP. RapidIO technology is available as Parallel RapidIO and Serial RapidIO (SRIO) in the RapidIO Verification IP from SmartDV. The RapidIO VIP comes with a comprehensive test suite that covers the majority of potential scenarios. It executes all conceivable protocol tests in a guided or extremely random manner, adding the potential to generate the most scenarios to successfully verify the DUT in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, etc.

Features

-

Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

-

Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

-

Supports 8b/10b and 64b/67b Encode and Decode functions.

-

Supports scrambler/Descrambler.

-

Supports 1.25 Gbaud, 2.5 Gbaud, 3.125 Gbaud, 5 Gbaud, 6.25 Gbaud, 10.3125 Gbaud, 12.5 Gbaud and 25.78125 Gbaud lane rate.

-

Supports 66, 50 and 34-bit addressing on the RapidIO interface.

-

Supports Parallel Physical 8/16 bits interfaces.

-

Supports all types of packets and sizes.

-

Supports all types of IDLE sequences, Control and Status Symbols.

-

Supports 8-bit, 16-bit and 32-bit device IDs.

-

Automatic freeing of resources used by acknowledged packets.

-

Supports I/O system, message passing and globally shared distributed memory (GSM).

-

Supports communication with mailboxes via messages.

-

Supports generation and reaction to flow control.

-

Supports out of order transaction delivery based on the prioritization.

-

Supports critical request flow ordering.

-

Very flexible to insert errors in serial lanes.

-

Supports Error Management Extensions.

-

Provides error injection and error detection with a wide variety of error types, which includes • Under and oversize packet. • CRC errors. • Invalid code group insertion. • Invalid /K/ characters insertion. • Lane Skew insertion. • Error on control symbol. • Unsupported packet types.

-

Supports cancellation and retrying of packets mechanisms.

-

Support all types of timing and protocol violation detection.

-

Supports constraints Randomization.

-

Status counters to keep track of various events, which includes • Corrupted/uncorrupted packets. • Corrupted/uncorrupted control symbols. • Type of packet. • CRC error. • Total number of errors detect

Deliverables

-

Complete testsuite to test every feature of RapidIO spec and also as per RIO LAB testsuite.

-

Examples showing how to connect various components, and usage of BFM and Monitor.

-

Detailed documentation of all class, task and functions used in verification env.

-

Documentation also contains User's Guide and Release notes

![]()