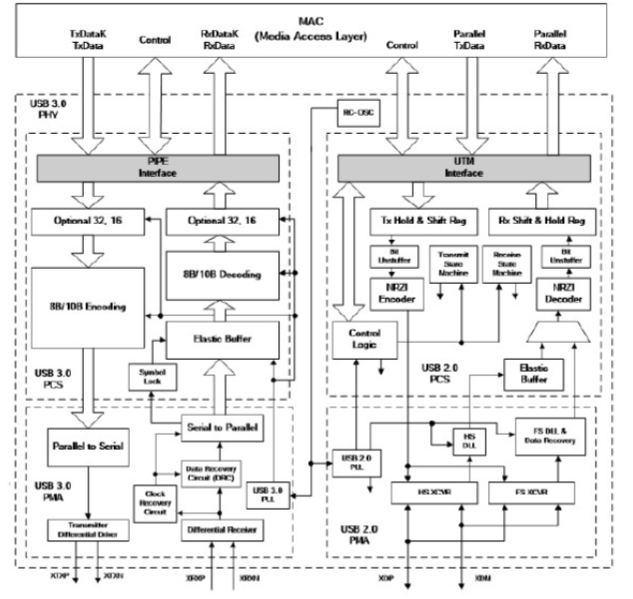

For auxiliary devices, a Universal Serial Bus (USB) transceiver is offered. The UTMI, USB 3.0, and USB 2.0 PIPE requirements are met by the PHY (USB SuperSpeed). The USB3.0 PHY IP transceiver is designed to consume little power and take up little space on the chip without compromising speed or data throughput. By providing a full on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, an integrated self-test module with built-in jitter injection, and a dynamic equalization circuit, the USB3.0 PHY IP delivers total support for high-performance designs. The USB3 MAC layer enables many IP sources to share a PHY interface (PIPE). Internal test monitoring and jitter are eliminated by constant power, built-in Jitter Injection Output, built-in Self-Test, and enabled customization of analogue circuit parameters.

Compliant with Universal Serial Bus 3.0 Specification

Supports 2.5GT/s and 5.0GT/s serial data transmission rate

Compliant with PIPE 3.0

Compliant with Universal Serial Bus 2.0 Specification

High-speed data transfer rate: 480 Mbps

Compliant with legacy USB 1.1

Full-speed data transfer rate: 12 Mbps

Compliant with UTMI 1.05 Specification

Operating Voltage: 1.1V and 3.3V

Support low jitter automatically calibrated oscillator for crystal-less mode

Support 125/250 MHz with 32/16-bit mode for USB 3.0

Support the Build-In-Self-Test (BIST) mode for low-cost TEG/ATE testing

Silicon Proven in TSMC 55LP.

Deliverables

Validation Reports Ensuring Layout Consistency and Rule Adherence

Layout Exchange Format Views for Placement and Routing Topology

Liberty Format Library for Timing, Power, and Noise Characterization

Verilog Model for Functional Simulation and Analysis

SDF Timing Specifications Applied to Circuit Connectivity Data

Insights and Recommendations for Successful Layout Execution

Verification Reports Confirming Layout Schematic and Design Rule Conformance