Description

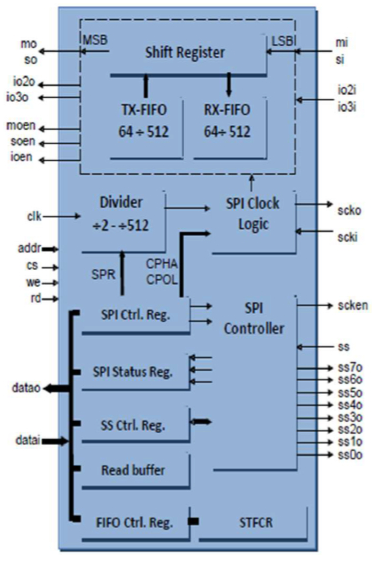

The SPI IP is a ground-breaking octal SPI that was created to provide the quickest operations for any serial SPI memory. It is adaptable enough to connect directly to several common product peripherals from different manufacturers. Additionally, the IP Core supports any 8, 16, and 32 bit CPU on the market. The SPI IP is a fully adjustable SPI master/slave device that lets you set the polarity and phase of the serial clock signal SCK. It makes it possible for the microcontroller to speak with serial peripherals and fast serial SPI storage. Additionally, it has the ability to communicate across processors in a multimaster system. The shifting and sampling of data on four serial data lines are synchronized by a serial clock line (SCK). Data is concurrently delivered and received in the Single SPI mode.

Features

-

Operates with 8, 16 and 32 bit CPUs

-

Full duplex synchronous serial data transfer

-

DMA support

-

Support for 32, 16 and 8 bit systems

-

Support for various system Bus Standards

-

Single, Dual, Quad and Octal SPI transfer

-

DDR support (Double Data Rate)

-

Multi master system supported

-

Optional FIFO size extension (128, 256, 512B)

-

Up to 7 SPI slaves can be addressed (more Slave Select Outputs can be added upon request)

-

Software Slave Select Output – SSO selection

-

Automatic Slave Select outputs assertion during each byte transfer

-

System error detection

-

Interrupt generation

-

Various Bit rates supported

-

Bit rate in fast SPI Mode ½ CLK

-

Four transfer formats

-

Simple SPU and DMA interface

-

Fully synthesizable, static synchronous de-sign with no internal tristates

Deliverables

-

Source code:

-

VHDL Source Code or/and

-

VERILOG Source Code or/and

-

Encrypted, or plain text EDIF

-

VHDL & VERILOG test bench environment

-

Active-HDL automatic simulation macros

-

Model Sim automatic simulation macros

-

Tests with reference responses

-

Technical documentation

-

Installation notes

-

HDL core specification

-

Datasheet

-

Synthesis scripts

-

Example application

-

Technical support

-

IP Core implementation support

-

3 months maintenance

-

Delivery of the IP Core and documentation updates, minor and

-

major versions changes

-

Phone & email support

Applications

-

Embedded microprocessor boards

-

Consumer and professional audio/video

-

Home and automotive radio

-

Low-power applications

-

Communication systems

-

Digital multimeter

![]()