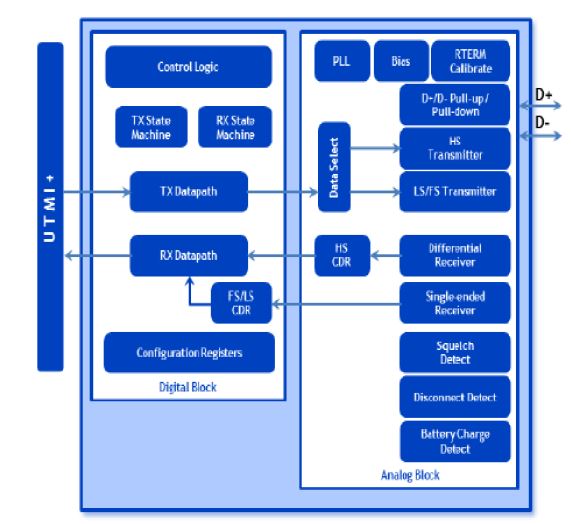

The USB2.0 PHY IP is an entire physical layer (PHY) IP solution built for high performance and low power consumption. For usage with either hosts, devices, or OTG function controllers, the USB2.0 IP implements a High-Speed USB 2.0 transceiver. The USB2.0 PHY IP is compatible with Full-Speed (12Mbps) and Low-Speed (1.5Mbps) data rates and complies with the UTMI+ level 3 specification. It integrates mixed-signal circuits to support High-Speed data rate at 480Mbps. The USB2.0 PHY IP also supports the additional USB Battery Charging requirements, which are aimed at mobile and consumer product applications. The USB2.0 PHY IP transceiver is designed to have a small chip size and low power consumption without compromising performance or data throughput. To enable complete support for host and device functionality, the USB2.0 PHY IP includes a full on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, a clock generating block provided by an internal PLL, and a resistor termination calibration circuit.

Deliverables

GDSII Format including Layer Assignments

Views of Placement and Routing Presented in .LEF Format

Standard Cell Library Featuring Timing and Power Information

Behavioral Model Expressed in Verilog Syntax

Netlist Including Timing Annotations in SDF Format

Recommendations for Effective Layout Design and Execution

Validation Reports Ensuring Layout Adherence to Schematic and Rules