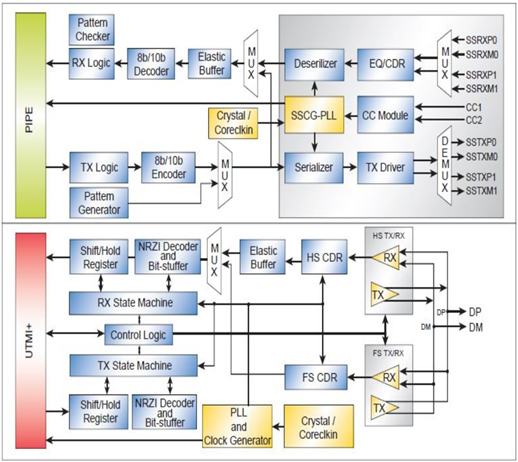

The USB 3.2 Gen2X1 transceiver IP supports all USB 3.2 Gen2X1 host and peripheral applications up to 10Gbps. It conforms with the standards of UTMI+ and PIPE4.0. The USB 3.2 Gen2X1 IP contains high-speed mixed signal circuits to handle Gen2 and Gen1 traffic and is backward compatible with high-speed data rates of 480Mbps, full-speed data rates of 12Mbps, and low-speed data rates of 1.5Mbps. The USB 3.2 Gen2X1 IP provides an active switch to enable bi-directional plug-in and particular functionality (such VBUS setup and USB attachment cable orientation identification) through the CC1/CC2 pins specified in the Type-C connection in order to support the USB Type-C connector.

Deliverables

Graphic Data System II File with Layer Allocation .

LEF Files Illustrating Placement and Routing Structures

Timing and Power Characteristics Repository in Liberty Format

Verilog Model Describing Circuit Functionality

Standard Delay Format Timing Constraints for Circuit Netlist

Application Notes Providing Layout Design Best Practices

LVS and DRC Verification Results Documentation