Description

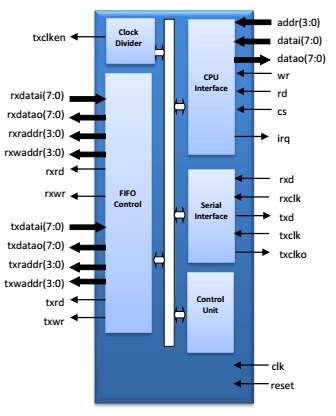

A popular HDLC transmission protocol is supported in a number of different ways by the HDLC IP Core. It controls address appending and detection during the bit stuffing operation. As if that weren't enough, this Core also offers CRC16 and CRC32 calculation. Thanks to the availability of separate receiver and transmitter FIFO buffers, maskable interrupt, and DMA interface request, the system performance is increased and CPU overload is decreased. Because the HDLC is a fully scalable IP Core, it is the ideal choice for high-end and deeply embedded projects. Small 8-bit SRAM-like interfaces, 32-bit complete AXI4 slave interfaces with burst support, AXI4Lite interfaces, and AHB and APB slave interfaces can also be given, depending on the demands of your project. The Frame Status Buffer is optional.

Features

-

Two separate receiver and transmitter interfaces.

-

Two separate, configurable FIFO buffers for receiver and transmitter

-

Bit stuffing and unstuffing

-

Address recognition for receiver and address insertion for transmitter

-

Two or one byte address field

-

CRC-16 and CRC-32 computation and checking

-

Collision detection

-

Byte alignment error detection

-

Programmable number of bits for idle detection

-

NRZI coding support

-

Shared flags, shared zeroes support

-

Pad fill with flags option

-

Transmitter clock generation

-

8-bit, 16-bit, 32-bit CPU interface

-

Interrupt output for handling control flags and FIFOs’ filling

-

Configurable core parameters

Deliverables

-

Source code:

-

VHDL Source Code or/and

-

VERILOG Source Code or/and

-

Encrypted, or plain text EDIF

-

VHDL & VERILOG test bench environment

-

Active-HDL automatic simulation macros

-

ModelSim automatic simulation macros

-

Tests with reference responses

-

Technical documentation

-

Installation notes

-

HDL core specification

-

Datasheet

-

Synthesis scripts

-

Example application

-

Technical support

Applications

-

CPU based applications with serial interface based on HDLC/SDLC protocol

-

Telecommunication

![]()