Description

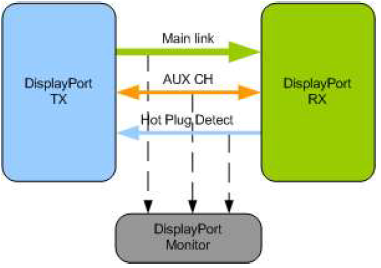

Display port 2.0 is the serial communication protocol developed by Video Electronics Standards Association(VESA) to support the video, audio and other data between a source device and sink device. Display port 2.0 VIP can be used to verify transmitter or Receiver device following the Display port basic protocol as defined in Display port 2.0. Display Port 2.0 Verification IP is supported natively in System Verilog, VMM, RVM, AVM, OVM, UVM, Verilog, System C, VERA, Specman E and non-standard verification env Display Port 2.0 Verification IP comes with optional Smart Visual Protocol Debugger which is GUI based debugger to speed up debugging.

Features

-

Full Display port 2.0 source device and sink device functionality.

-

Supports backward compatibility with previous versions upto DPv1.4a

-

Supports control symbols for framing.

-

Supports Interlaced & non-interlaced video stream.

-

Supports main link, Aux link and Hot plug functionality.

-

Supports Fast and Full link training.

-

Supports skip the link training.

-

Supports Spread Spectrum clocking (SSC).

-

Supports I2C over AUX CH to access EDID, Display ID.

-

Supports Symbol Stuffing and Transfer Unit.

-

Supports ANSI8B10B encoding / decoding.

-

Supports 128b/132b channel coding

-

Supports Serialization and de-serialization.

-

Supports RGB, YCBCR444, YCBCR422, YCBCR420 and Y-only RAW color format.

-

Supports Main Stream Attribute (MSA) packets.

-

Supports following Secondary packets, • Audio timestamp, Audio stream, Extension • Audio copy management, ISRC, VSC • VSC extension VESA, VSC extension CEA/CTA • Adaptive-Sync SDP

-

Supports packing of all audio formats supported by IEC 60958-1, IEC 60958-3, IEC 60958-4, IEC 61937-1, IEC 61937-3, CEA 861-F/CTA-861, CEA 861.2/CTA- 861.2, CEA-861.3/CTA-861.3,CEA 861-G

-

Sequence(128b132b_TPS1,128b132b_TPS2,TPS1,TP S2,TPS3 and TPS4).

-

Supports GTC-based video timing synchronization

-

System version2.2 (HDCP v2.2)

-

Supports for HDCP2.2 with full authentication.

-

Supports High-bandwidth Digital Content Protection

-

Detects and reports the following errors, • Invalid control character, Invalid data character • Invalid 10bit code, Sync errors, Scrambler errors • Supports LT-tunable Phy Repeater(LTTPR).

-

Supports Horizontal Blanking Expansion

-

Supports jitter insertion for Main link Clock and Aux Channel Clock

-

Supports RBR, HBR, HBR2, HBR3, UHBR10, UHBR20, UHBR13.5

-

Monitors, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

-

Status counters for various events on bus.

-

Callbacks in node transmitter, receiver and monitor for user processing of data.

Deliverables

-

Complete regression suite containing all the Display port testcases.

-

Examples showing how to connect various components, and usage of Transmitter, Receiver and Monitor.

-

Detailed documentation of all class, task and function's used in verification env.

-

Documentation contains User's Guide and Release notes

![]()