Description

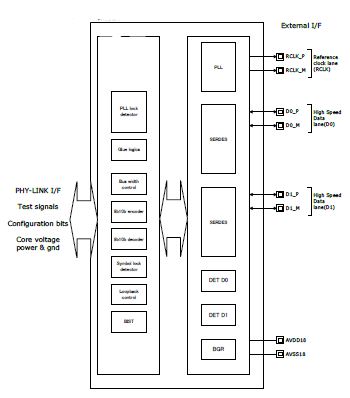

SD4.1 UHS-II IP utilizes distinctive SerDes technology to attain a speed of 312MB/s for UHS-II while maintaining low power consumption. This PHY IP is versatile, suitable for use on both the device and host sides, including SDIO. Therefore, it can be integrated into SOCs for a wide range of applications such as SD cards, digital cameras, digital videos, digital TVs, media players, and personal computers.

Features

-

SD 4.1 compliant SDHC/SDXC UHS-II Physical Layer for Host

-

16bit interface to Link layer

-

Supports both Full Duplex mode and Half Duplex mode

-

Wide range channel speed up to 1.56Gbps

-

Power saving mode

-

Configurable analog characteristics

-

Driver swing voltage

-

Testability:Built-in scan test

-

Area: <1mm2

-

Process: - SAMSUNG14nm 1.8V/0.8V

Deliverables

-

Datasheet

-

Integration guideline

-

GDSII or Phantom GDSII

-

Layer map table

-

CDL netlist for LVS

-

LEF

-

Verilog behavior model

-

Liberty timing model

-

DRC/LVS/DRC results

-

Verilog RTL or netlist of digital part

![]()