Description

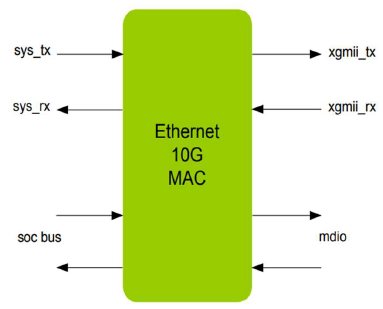

The Ethernet 10G MAC IP Core is full-featured, easy-to- use, synthesizable design that is easily integrated into any SoC or FPGA development. The Ethernet 10G MAC IP can be implemented in any technology. The Ethernet 10G MAC IP core supports the Ethernet protocol standard of IEEE 802.3.2018 specification. It can also supports a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses . The Ethernet 10G MAC IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The Ethernet 10G MAC IP is validated using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Features

-

Compliant with IEEE Standard 802.3-2018 specification

-

Supports full duplex mode of operation

-

Supports standard 10Gbps Ethernet link layer data

-

Supports XGMII interface operating at 156.23MHz

-

Supports Programmable Inter Packet Gap and Preamble length

-

Supports MDIO (Clause 22 and Clause 45) Interface

-

Supports start control character alignment

-

Provides detailed statistics as per specification

-

Supports Jumbo Frame

-

Supports Loopback functionality

-

Supports transmit and receive FIFO interface

-

Supports FCS(CRC) transmission and reception

-

Supports Pause frame based flow control

-

Supports IEEE Standard 802.3az Energy Efficient Ethernet(EEE)

-

Supports IEEE Standard 802.1Q and IEEE Standard 802.1ad VLAN

-

Supports Wake-on-LAN

-

In house UNH compliance tested

-

Optional support for TCP/IP

-

Optional support for IEEE Standard 1588-2008 PTP

-

Optional support for DMA support for both transmit and receive side

-

Optional support for the following HiGig features • HiGig • HiGig+ • HiGig2 • HiGigLite • 2.5G HiGig

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices

-

Synchronization as per IEEE Standard 1588-2008(PTP) and IEEE Standard 802.1AS(GPTP)

Deliverables

-

RTL design in Verilog

-

Lint, CDC, Synthesis Scripts with waiver files

-

Lint, CDC, Synthesis Reports

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Technical documentation in greater detail

-

Easy to use Verilog Test Environment with Verilog Testcases

![]()