Description

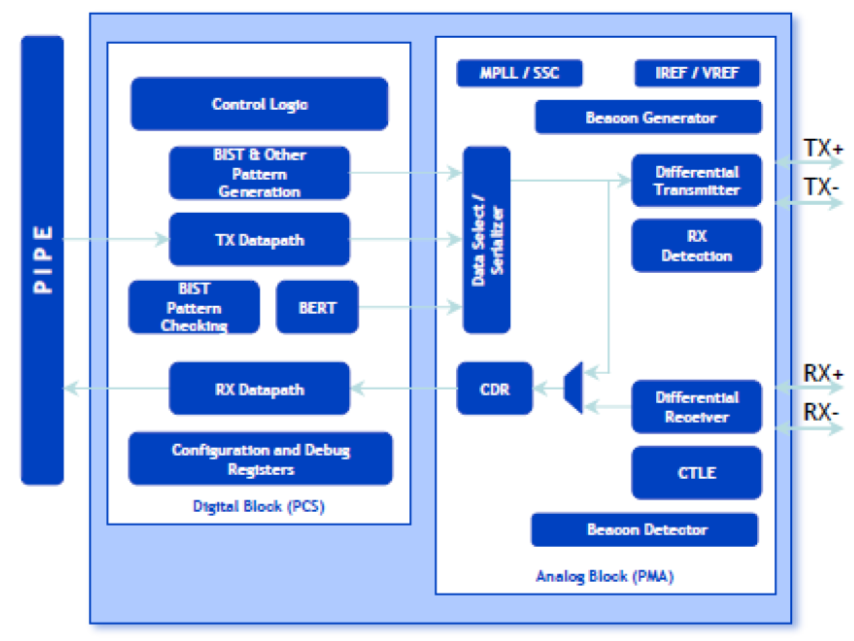

The PCIe2.0 PHY IP is an all-in-one physical layer (PHY) IP solution for mobile and consumer applications. The PHY IP includes mixed-signal circuits to handle both 2.5GT/s and 5.0GT/s data transfer speeds while adhering to the PCIe2.0 basic standards. The PCIe2.0 PHY IP is made up of two layers: the Physical Media Attachment (PMA) layer and the Physical Coding Sublayer (PCS), and it simply links to either the PCIe2.0 MAC layer via the standard PIPE-3.0 interface.

The PCIe2.0 PHY IP transceiver is optimized for low power consumption and minimal die area, without sacrificing performance and high-data throughput. The PCIe2.0 PHY IP comprises a complete on-chip physical transceiver solution with Electrostatic Discharge (ESD) protection, built-in self-test module with embedded jitter injection, and a dynamic equalization circuit that ensures full support for highperformance designs.

Features

-

Compatible with PCIe base Specification

-

Full compatible with PIPE4.2 interface specification

-

Independent channel power down control

-

Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

Support 16-bit/32bit parallel interface

-

Support for PCIe gen1(2.5Gbps) and PCIe gen2(5.0Gbps)

-

Support flexible reference clock frequency

-

Support 100MHz differential reference clock input or output (with SSC optionally) in PCIe Mode

-

Support Spread-Spectrum clock (SSC) generation and receiving from -5000ppm to 0ppm

-

Support programmable transmit amplitude and Deemphasis

-

Support TX detect RX function in PCIe Mode

-

Support Beacon signal generation and detection in

-

Production test support is optimized through high coverage at-speed BIST and loopback

-

Integrated on-die termination resistors and IO Pads/Bumps

-

Embedded Primary & Secondary ESD Protection

-

ESD: HBM/MM/CDM/Latch Up 2000V/200V/500V/100mA

-

Silicon Proven in TSMC 22ULP

Deliverables

-

GDSII & layer map

-

Place-Route views (.LEF)

-

Liberty library (.lib)

-

Verilog behaviour model

-

Netlist & SDF timing

-

Layout guidelines, application notes

-

LVS/DRC verification reports

![]()