Description

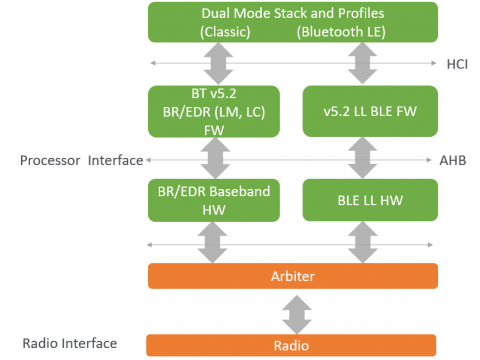

This Baseband Controller IP core is a composite HW-FW implementation of the Classic Bluetooth specifications and Bluetooth Low Energy v5.3 Specifications.

Compatible with the standard Bluetooth HCI, it can be used with any Bluetooth dual mode 5.3 host software protocol stack and profiles, either split around the HCI so that the lower layers and upper layers can run on different processors or systems, or combined together to run on the same processor to make a fully hosted solution. The feature set for supporting headset solution (including TWS) has been prioritized.

-

Will support 2 connections Power Considerations

-

The IP will provide the hooks to ensure power save mechanisms in the SoC

-

Power gating, clock gating and maintaining a low power domain during sleep are basic hooks

-

Protocol based features like adaptive window widening and slave latency will be supported.

-

The IP has always been architected to minimize the uptime of RF

Features

-

Software Memory footprint (ARM Cortex M0/M3): ROM ~ 300KB ; RAM ~ 112 KB

-

Combined Hardware gate count : 250 k gates

-

Arbitration logic implemented in hardware and assisted by software

-

Baseband and LE LL Accelerator

-

Discovery / Connection / Role Switch procedures

-

LE Advertising/Scanning/Connection procedures

-

Baseband level flow control, ACK handling & retransmissions

-

Power Save: Sleep mode - clock shut down for core hardware modules, except clock & power management block.

-

Deep sleep mode - clock shutdown to all modules. Bluetooth clock is maintained in 32KHz domain. External RF modem chip can also be shutdown.

-

Shutdown – Entire baseband clock can be shutdown by firmware. External RF modem chip can also be shutdown. Enables power gating.

Deliverables

-

Synthesizable Verilog RTL

-

Behavioral models

-

Module test bench and testcases

-

ASIC and FPGA synthesis scripts

-

BlueWiz FPGA platform

-

Flash download utility

-

HCI Commander – HCI application

-

BlueWiz Architecture document

-

BlueWiz Verification document

-

SoC integration approach note

-

User manuals for development tools

-

HCI/LM/LC/LL firmware source code in C

-

Transport drivers (UART, USB)

-

Platform drivers for development platform

-

OSAL for MINT OS/FreeRTOS

Benefits

-

MINIMUM MIPS: Hardware sustains a link in its current state, so firmware overhead only for PDU and data exchange. Hardware also sustains all type of logical links

-

MAXIMUM INTERRRUPT LATENCY TOLERANCE

-

MINIMUM INTERRUPT PROCESSING TIME: Split of time critical and non time critical functions. Non time critical functions handled in task context using MINT OS tasking architecture

-

EFFICIENT HARDWARE/SOFTWARE PARTITIONING: Reduced interaction between firmware and hardware. Reduce bus activity

-

ACTIVE AND LOWPOWER MODE CLOCK GATING

-

FIRMWARE & HARDWARE TESTABILITY: Access to key firmware data structures, lower layers (like LMP) to bypass normal functional path, BB register through vendor commands

-

LOGGER: Real time dump of firmware, baseband and RFIC status. Log of assertions embedded in firmware

Applications

-

smart phones

-

ear buds, headsets, speakers

-

tablets

-

gaming

-

remote control

![]()