Description

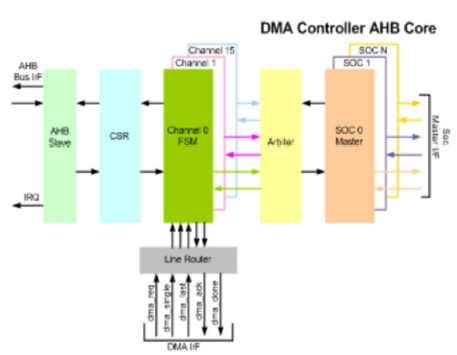

DMA Controller with AHB interface is full featured, easy-to-use, synthesizable design that can be used with AHB based systems as a controller to transfer data directly from system memory to IP core or from IP core to system memory. Through its compatibility, it provides a simple interface to any IP core with the appropriate logic in between.

Features

-

Supports 1-16 channel DMA Transmit and DMA Receive Engine

-

Compliant with ARM AMBA 2 AHB, AMBA 3 AHB-Lite and AMBA 5 AHB Specification

-

Supports access for Ring and Chained Descriptor Structures

-

Configurable Transmit and Receive Engine based on Host Memory Data Width

-

Configurable support by DMA Transmit and Receive Engine for both of the endianness of the host memory (Little / Big Endian)

-

Supports hardware DMA Control registers that can be written and read by CPU

-

Round Robin algorithm for arbitration between DMA Transmit and Receive Engine to access SOC Master Bus

-

SOC Master bus can be AXI/ AHB/ APB/ OCP/ Tilelink/ Wishbone

-

Supports AHB Slave bus

-

Uses SOC Slave Interface to get Receive and Transmit descriptors and transfer the data to/from the system memory from/to FIFO inside the DMA controller

-

User logic to map data fetched from Host to IP core or from IP core to host

-

Supports Sideband DMA request and Grant based triggering of transfers as on option for peripherals

-

Supports Scatter Gathers list

-

Supports 8/16/32 bit wide data transfers

-

Supports QoS per channel if SOC master interface supports Qos.

-

Supports programmable burst capability per SOC master

-

DMA supports full duplex operation, processing read and write transfers at the same time

-

Supports Link list-based processor for autonomous operation

-

Interface widths can be controller for each SOC master interface

-

Supports configurable DMA Transmit and DMA Receive FIFO based on Host Memory Data width

-

Generate full 32-bit addresses on the SOC master interface.

Deliverables

-

The DMA Controller with AHB interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes

![]()