Description

The DDR4/3 PHY is compatible with JEDEC DDR3 and JEDEC DDR4 SDRAMs, supports a range of DDR3 DRAM speeds from 666Mbps to 2133Mbps and DDR4 DRAM speeds from 1866Mbps to 2400Mbps, and target support x16 DDR3/DDR4 SDRAM components, the design include an analog hard macro (CLK/CMD/ADDR/DQ/DQS) and a synthesizable digital design. It supports software auto training includes read gate, read/write data eye timing, and PHY Vref settings. Supports DDR4/DDR3 SDRAM.

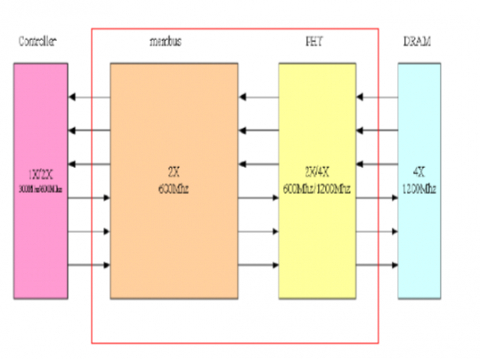

Optimized for high performance, low latency, low area, low power, and ease of integration, the DDR4/3 PHY is provided as a hard DDR PHY that is primarily delivered as GDSII including integrated application-specific DDR4/3 I/Os. Supporting the GDSII-based PHY is the RTL-based PHY. The DDR4/3 PHY includes a DFI 4.0 interface to the memory controller and can be combined with controllers for a complete DDR (Double Data Rate) interface solution

Features

-

Supports DDR4/DDR3 SDRAM

-

DDR4 JEDEC standard 1.2v I/O (POD_12 I/O)

-

DDR3 JEDEC standard 1.5v I/O (SSTL_15-compatible)

-

16 bits width, Single Channel DDR4/DDR3 SDRAM Interface.

-

16 bits for per channel, could support 2 x8 bits DDR3

-

Memory Clock up to 600MHz, DFI Clock up to 600MHz.

-

Support DDR3 800/1066/1333/1600/1866/2133Mbps; DDR4 1866/2133/2400Mbps

-

Supports DFI like interface

-

4-bit pre-fetch architecture

-

DLL Lock for 1200MHz

-

Supports SW DDR training

-

Supports DDR IO loopback test

-

Providing per bit de-skew function

-

Supports DDR3 DLL disable mode (CL6/CWL6)

-

Supports DDR3 CL=6 ~ CL17

-

Supports DDR3 CWL=6, CWL=11

-

Supports DDR3 Burst length 4/8

-

Supports DDR3 DQ write Mask Mode

-

Supports DDR3 Read, Write eye training

-

Supports DDR4 CL=9~ CL30, DDR4 CWL=9~CWL21

-

Supports DDR4 DLL disable mode, Read DBI Mode

-

Supports DDR4 DQ write Mask Mode

-

Supports DDR4 Connectivity Test Mode

-

Supports DDR4 Even parity check Mode

-

Supports DDR4 Read gated training

-

Supports DDR4 Read eye training, Write eye training

-

Supports DDR4 TX/RX Vref training

-

Supports DDR Retention mode

-

Supports DQ TX/RX per-bit deskew

-

Programmable On-die Termination on I/O

-

Programmable data-output drive strength I/O

-

DDR4/DDR3 impedance calibration

-

0.9V Core Power supply

-

1.2V DDR4 IO Power supply

-

1.5V DDR3 IO Power supply

-

Support software DDR training

-

DDR3 training: support RX_GATED training, per-bit de-skew for RX/TXpath, DQ RX eye training and DQ TX eye training

Benefits

-

Low Power

-

Low Area

-

Low Latency

-

JEDEC, the standards body responsible for memory standards has defined and developed DRAM categories such as DDR: DDR, DDR2/3/4 mobile DDR: LPDDR2/3/4 high bandwidth DRAM: HBM, HBM2/2E/3)

-

matching Controller in production

-

supports both 16bits and 32 bits

Applications

-

SSD Controller

-

Digital TV

-

Mobile

-

Multimedia

-

Setup Box

-

Data centers (networking and storage)

-

Servers

-

High-performance computing

-

IOT

-

Surveillance

Deliverables

-

User Manual

-

Behavior model, and protected RTL codes

-

Protected Post layout netlist and Standard

-

Delay Format (SDF)

-

Frame view (LEF)

-

Metal GDS (GDSII)

-

Test patterns and Test Documentation