Description

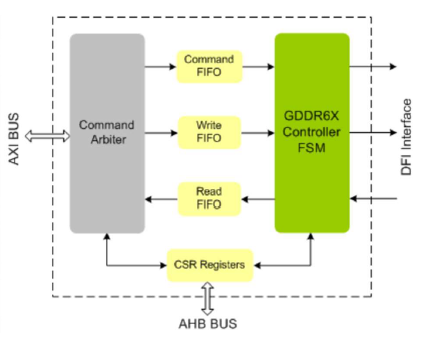

GDDR6X interface provides full support for the GDDR6X interface, compatible with GDDR6X protocol draft specification and DFI-version 4.0 or 5.0 Specification Compliant. Through its GDDR6X compatibility, it provides a simple interface to a wide range of low-cost devices. GDDR6X IP is proven in FPGA environment. The host interface of the GDDR6X can be simple interface or can be AMBA AHB, AMBA AHB-Lite, AMBA APB, AMBA AXI, AMBA AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or Custom protocol.

Features

-

Supports GDDR6X protocol draft specification.

-

Compliant with DFI-version 4.0 or 5.0 Specification.

-

Supports all the GDDR6X commands as per the specs.

-

Supports up to 16 AXI ports with data width upto 512 bits.

-

Supports controllable outstanding transactions for AXI write and read channels

-

Supports in port arbitration and multi port arbitration.

-

Supports user programmable page policy. • Closed page policy • Open page policy

-

Supports 2 separate independent channels with point-to-point interface for data, address and command.

-

Supports Double Data Rate (DDR).

-

Supports up to 8GB device density.

-

Supports X8 and X16 Mode.

-

Supports Programmable READ/WRITE latency.

-

Supports Bank grouping and 16 internal banks per channel.

-

Supports Data bus inversion (DBI) & Command Address bus inversion (CABI).

-

Supports Read/Write data transmission integrity secured by cyclic redundancy check.

-

Supports WRITE Data mask function (single/double byte mask).

-

Supports Programmable EDC hold pattern for CDR.

-

Supports Programmable CRC READ/WRITE latency.

-

Supports Low Power modes.

-

Supports Auto refresh & self-refresh modes.

-

Supports On-die termination operation.

-

Supports Vendor ID for device identification.

-

Supports COMMAND ADDRESS, WCK2CK,READ/WRITE Training mode’s.

-

Supports IEEE.1149.1 boundary scan operation.

-

Supports all mode registers programming.

-

Supports for power down features.

-

Supports programmable clock frequency of operation.

-

Fully synthesizable

-

Static synchronous design.

-

Positive edge clocking and no internal tri-states.

-

Scan test ready

-

Simple interface allows easy connection to microprocessor/microcontroller devices

Deliverables

-

The GDDR6X interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()