Description

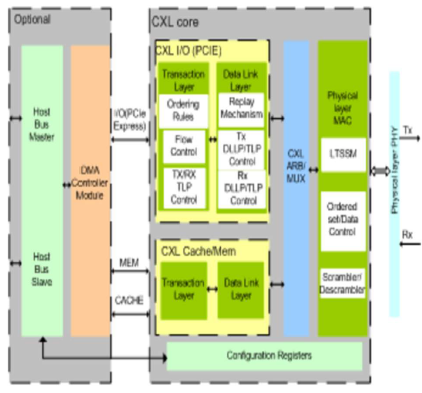

The CXL Controller IP core supports the CXL 1.0 and 1.1 Specification. Through its CXL compatibility, it provides a simple interface to a wide range of lowcost devices. CXL Controller IP is proven in FPGA environment. The host interface of the CXL Controller can be simple interface or can be AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

Features

-

Compliant with CXL 1.0/1.1 Specifications

-

Supports Native PCIe mode and below features as defined in the PCIe specification • PCIE Express specs 1.0/2.0/3.0/4.0/5.0 • PIPE interface • Full PCIE Controller functionality • Supports ASPM and Software controlled Power Management • Supports Speed and Link Width negotiation • Supports Up configure, polarity inversion, and lane-to-lane skew

-

Supports static configuration of PCIe vs CXL protocol mode

-

Supports the signaling rate of 8 GT/s, 16 GT/s or 32 GT/s for CXL mode

-

Supports link width support for x16, x8, x4, x2, and x1 (degraded mode) in CXL mode

-

Bifurcation (aka Link Subdivision) support to x4 in CXL mode

-

Implements CXL.io, CXL.mem, and CXL.cache

-

Supports ARB/MUX Link Management Packets

-

Supports CXL Power Management VDM Packets

-

Supports arbitration and data multiplexing/demultiplexing

-

Supports following CXL.cache/CXL.mem slots, • Header slot • Generic request/response slot • Generic data slot

-

Supports following CXL cache line, • 32B Half cache line • 64B Full cache line

-

Supports following CXL flit type encoding, • Protocol type • Control type

-

Supports all CXL.cache/CXL.mem request and response messages

-

Supports all snoop responses

-

Supports various framing errors

-

Supports Multiple Data Header (MDH)

-

Supports byte enable

-

Supports CXL.cache/CXL.mem link layer retry

-

Supports type 1, type 2 and type 3 CXL Devices

-

Supports implied EDS token

-

Supports Address Translation Service (ATS)

-

Supports configurable TC to VC queue mapping

-

Supports data poisoning

-

Supports virtual channel management

-

Supports DMA(Optional)

Deliverables

-

The CXL Controller interface is available in Source and netlist products.

-

The Source product is delivered in Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()