Description

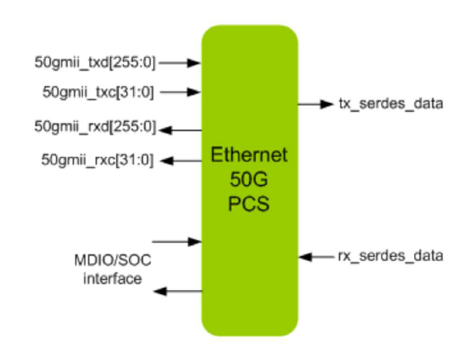

Ethernet 50G PCS core is compliant with IEEE Standard 802.3.2018 Ethernet specification. Through its Ethernet compatibility, it provides a simple interface to a wide range of low-cost devices. Ethernet 50G PCS IP is proven in FPGA environment. It can also support a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses.

Features

-

Supports IEEE Standard 802.3.2018

-

Supports 50G BASE-R

-

Supports 50G BASE KR2/CR2

-

Supports 64b/66b encoding and decoding for transmit and receive path

-

Supports data scrambling on the transmit path and descrambling on the receive path

-

Supports Lane Distribution across 4/2 Lanes for 50Gpbs

-

Supports Block synchronization

-

Supports gearbox for various data width

-

Supports Alignment Marker insertion and removal

-

Support PCS Lane Deskew

-

Supports BIP-8 insertion on transmit path and checking on receive path per lane

-

Supports Bit Error Rate monitoring

-

Supports receiver Link fault status detection

-

Supports Loopback functionality

-

Supports for IEEE 802.3az Energy Efficient Ethernet.

-

Supports Configurable Management Interface (MDIO - Clause 45 / SOC Bus)

-

Supports PMA interface for the following data widths, • 32 • 40

-

Supports RS FEC as per clause 108 of IEEE Standard 802.3.2018

-

Optional support for Base-R FEC as per clause 74 of IEEE Standard 802.3.2018

-

Programmable PRBS32 and PRBS9 test pattern generators and error checker

-

Optional support for auto negotiation for backplane Ethernet as per clause 73 of IEEE Standard 802.3.2018

-

Optional support for link training as per clause 72 of IEEE Standard 802.3.2018

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices

Deliverables

-

Implementing the Verilog RTL design practically

-

Integration of waivers into validation scripts to encompass Linting, CDC analysis, and Synthesis

-

Detailed and comprehensive reports offering extensive insights into Linting, CDC analysis, and Synthesis methodologies

-

Leveraging IP-XACT RDL for efficient address map generation

-

Unifying firmware code and Linux drivers into a cohesive and integrated package

-

Exhaustive technical documentation thoroughly covering all facets and elements

-

Verilog Test Environment seamlessly integrating intuitive and coherent test cases

![]()