Description

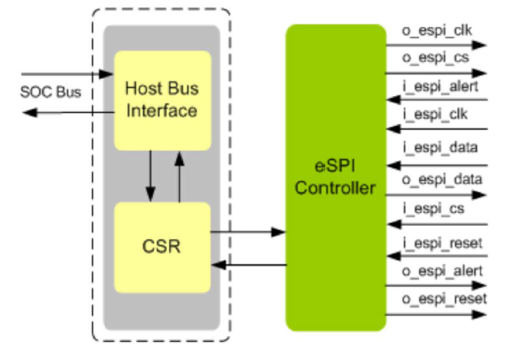

The eSPI controller has a comprehensive feature set, is simple to use, can be synthesized, and is compliant with the eSPI standard protocol. It gives a variety of inexpensive devices a straightforward interface thanks to its eSPI compatibility. In an FPGA context, ESPI controller IP has been tested. The eSPI controller's host interface options include a basic interface, AMBA APB, AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone, or a custom protocol. Verilog and VHDL both natively support eSPI Controller IP.

Features

-

Compliant with eSPI base specification as defined in Enhanced Serial Peripheral Interface (eSPI) Specification rev.1.0.

-

Supports Master and Slave Modes

-

Supports Single, Dual and Quad modes

-

Supports TX and RX operation as per specs

-

Supports below transaction phases • Command Phase • Turn-Around Phase • Response Phase

-

Supports baud rate selection

-

Supports Slave triggered transaction

-

Supports Power management Event

-

Supports Interrupts and Alert

-

Supports In-band reset

-

Supports below multiple channels • Peripheral Channel • Virtual Wires Channel • OOB Message (Tunnelled SMBus) Channel • Run-time Flash Access Channel

-

Various kind of Master and Slave errors detection and handling

-

Supports CRC checking

-

Fully synthesizable.

-

Static synchronous design.

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices

Deliverables

-

The eSPI CONTROLLER interface is available in Source and netlist products.

-

The Source product is delivered in Verilog. If needed, VHDL and SystemC can also be provided

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()