Description

The serial communication protocol created for use with ADC and DAC is called JESD204 (Serial Interface for Data Converttors). To confirm that a transmitter or receiver device is adhering to the JESD204 basic protocol as specified in JESD204, utilize the JESD204A/B/C VIP. It is compatible with all Verilog simulators that support SystemVerilog and the Verilog HDL environment. SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E, and non-standard verification environments all natively support JESD204 Verification IP. The Smart Visual Protocol Debugger (Smart ViPDebug), a GUI-based debugger that speeds up debugging, is an optional addition to the JESD204 Verification IP.

Features

-

Follows JESD204 specification JESD204A, JESD204B and JESD204C

-

Supports Transmitter and Receiver Mode.

-

Supports up to 32 lanes.

-

Supports 32bit data width per converter.

-

Supports up to 256 converters per transmitter & receiver BFM.

-

Scrambler can be enabled or disabled.

-

Supports 8b/10b link layer functions.

-

Supports 64b/66b link layer functions based on IEE802.3 Clause 49 and JESD204C.

-

Supports 64b/80b link layer functions with fill bit encoding based on IEEE802.3 clause 49 and JESD204C.

-

Supports Forward Error Correction (FEC) and command channel.

-

Supports following cyclic redundancy checks (CRC) encoding in JESD204C.

-

CRC-3

-

CRC-12

-

Supports single block, Multi block and extended multi block.

-

Provides error injection and error detection with a wide variety of error types. Which includes,

-

Invalid code group insertion

-

Disparity errors

-

CRC errors

-

Sync error insertion

-

Lane skew insertion

-

FEC errors

-

Scrambler error insertion

-

Supports constraints Randomization.

-

Functional coverage to cover each and every feature of the JESD204 specification.

-

Test suite to test each and every feature of JESD204 specification.

-

Call-backs monitor, transmitter and receiver for various events.

-

Status counters for various events on bus.

Deliverables

-

Complete regression suite containing all the JESD204 testcases.

-

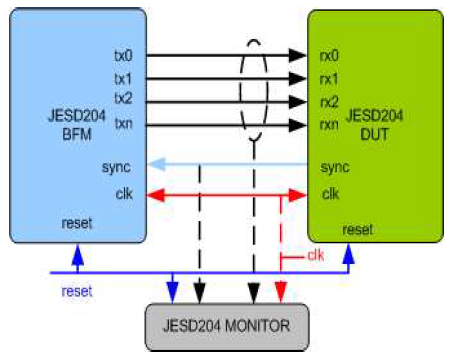

Examples showing how to connect various components, and usage of Transmitter, Receiver and Monitor.

-

Detailed documentation of all class, task and functions used in verification env.

-

Documentation contains User's Guide and Release notes

![]()