Description

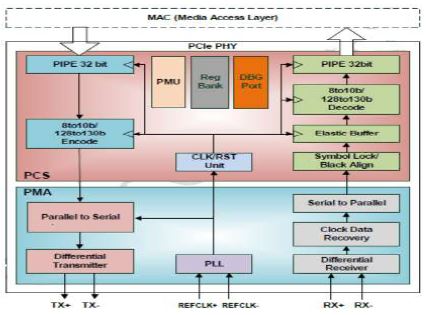

This Peripheral Component Interconnect Express (PCIe) x4 PHY is compliant with PCIe 5.0 Base Specification with support of PIPE 5.1 interface spec. Lower power consumption is achieved due to support of additional PLL control, reference clock control, and embedded power gating control. Also, since a fore mentioned low power mode setting is configurable, the PHY is widely applicable for various scenarios under different consideration of power consumption.

The PHY meets the needs of today’s high-speed chipto-chip, board-to-board, and backplane interfaces while being extremely low in power and area. Verification PCIe PHY functionality is verified in NCVerilog simulation software using test bench written in Verilog HDL.

Features

-

Compliant with PCIe 5.0 Base Specification

-

Compliant with PIPE 5.1

-

Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s, 16.0 GT/s and 32GT/s

-

Supported physical lane width: x4

-

Supported parallel interface: 16/32- bit(Gen4/5), 10/20-bit(Gen1/2/3)

-

Support dual-port PLL with LC tanks

-

Support CC/SRIS/SRNS

-

Support SSC for EMI reduction

-

DFE+CTLE for RX-EQ training

-

3-tap FFE for TX preset

-

Power-gated for lowest leakage in L1.2 low power mode(PMA)

-

Auto power saving for short reach

-

TSMC 12nm FFC 1P10M (ULVT/SVT) process

-

Operating Voltage: 0.8V and 1.2V

-

Built-in EYE-monitor and EYE checker

Benefits

-

Supports all required features of the PCIe® 5.0, 4.0, 3.1, 2.1, 1.1, and PIPE specifications

-

x1, x2, x4, x8, x16 lane configurations with bifurcation

-

Power-gated for lowest leakage in L1.2 low

-

power mode(PMA)

-

Auto power saving for short reach

-

Supported parallel interface: 16/32- bit(Gen4/5), 10/20-bit(Gen1/2/3)

-

PCIe PHY functionality is verified in NCVerilog simulation software using test bench written in Verilog HDL

Applications

-

SSD Controller

-

Digital TV

-

Setup Box

-

Desktops, workstations, servers

-

Automotive

-

Embedded systems and set-top boxes

-

Network switches and routers

-

Enterprise computing and storage networks

Deliverables

-

Application Note / User Manual

-

Behavior model, and protected RTL codes

-

Protected post layout netlist and Standard Delay Format (SDF)

-

Synopsys library (LIB)

-

Frame view (LEF)

-

Metal GDS (GDSII)

-

Test patterns and Test Documentation

![]()